## Vision Chips or Seeing Silicon

### Third Revision

### Alireza Moini March 1997

The Centre for High Performance Integrated Technologies and Systems

The University of Adelaide SA 5005, Australia

Tel: 61 8 8303 3403 Fax: 61 8 8303 4360

Email: moini@eleceng.adelaide.edu.au

Department of Electronics Engineering The University of Adelaide SA 5005, Australia

http://www.eleceng.adelaide.edu.au/Groups/GAAS/Bugeye/visionchips/index.html

Revision 3.5 Copyright ©1995-1997 Alireza Moini All Rights Reserved

### Vision Chips or Seeing Silicon

### Alireza Moini

The Centre for High Performance Integrated Technologies and Systems

Department of Electrical & Electronics Engineering

The Univ. of Adelaide, SA 5005, Australia

Tel: +61 8 8303 3403, Fax: +61 8 8303 4360

email: moini@eleceng.adelaide.edu.au

WWW: http://www.eleceng.adelaide.edu.au/Personal/moini/

March 1997

### Contents

| 1 | $\operatorname{Intr}$ | oduction                                              | 5  |

|---|-----------------------|-------------------------------------------------------|----|

|   | 1.1                   | Smart sensors                                         | 5  |

|   | 1.2                   | Advantages and disadvantages of vision chips          | 6  |

|   | 1.3                   | Challenges                                            | 7  |

|   | 1.4                   | Technology                                            | 8  |

|   |                       | 1.4.1 CMOS                                            | 8  |

|   |                       | 1.4.2 BiCMOS                                          | 9  |

|   |                       | 1.4.3 CCD and CMOS/CCD                                | 9  |

|   |                       | 1.4.4 GaAs MESFET and HEMT                            | 10 |

|   | 1.5                   | Major groups working on vision chips                  | 10 |

|   | 1.6                   | How vision chips are presented in this report         | 12 |

|   | $\mathbf{Acl}$        | knowledgments                                         | 14 |

| 2 | Spa                   | tial Vision Chips                                     | 16 |

|   | 2.1                   | Introduction                                          | 16 |

|   | 2.2                   | Mahowald and Mead's silicon retina                    | 18 |

|   | 2.3                   | Mead's adaptive retina                                | 19 |

|   | 2.4                   | Mahowald and Delbrück's stereo matching chips         | 20 |

|   | 2.5                   | Bernard et al.'s Boolean artificial retina            | 22 |

|   | 2.6                   | Andreou and Boahen's silicon retina                   | 23 |

|   | 2.7                   | Kobayashi et al.'s image Gaussian filter              | 24 |

|   | 2.8                   | PASIC sensor from Linköping University                | 26 |

|   | 2.9                   | MAPP2200 sensor from IVP                              | 28 |

|   | 2.10                  | Forchheimer-Åström's NSIP sensor                      | 28 |

|   | 2.11                  | Sandini et al.'s foveated CCD chip                    | 29 |

|   | 2.12                  | IMEC-IBIDEM's foveated CMOS chip                      | 31 |

|   | 2.13                  | Wodnicki et al.'s foveated CMOS sensor                | 32 |

|   | 2.14                  | Standley's orientation detection chip                 | 33 |

|   | 2.15                  | Harris et al.'s Resistive Fuse Vision Chip            | 35 |

|   | 2.16                  | DeWeerth's Localization and Centroid Computation Chip | 38 |

|   | 2.17                  | Ward & Syrzycki's Receptive Field Sensors             | 40 |

|   | 2.18                  | Wu & Chiu's 2D Silicon Retina                         | 42 |

|   | 2.19                  | Nilson et al.'s Shunting Inhibition Vision Chip       | 43 |

|   | 2.20                  | Keast & Sodini's CCD/CMOS Imager and Processor        | 44 |

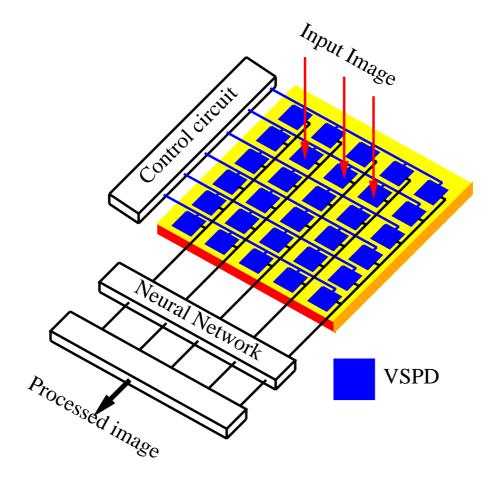

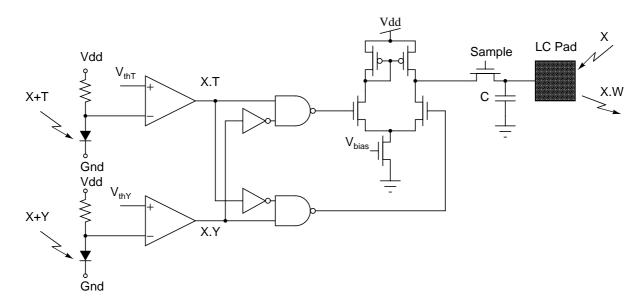

|   | 2.21                  | Mitsubishi Electric's CMOS Artificial Retina with VSP | 46 |

|   | 2.22                  | Venier et al.'s Solar Illumination Monitoring Chip    | 47 |

| 3 | Spat         | tio-Temporal Vision Chips                                               | <b>49</b> |   |

|---|--------------|-------------------------------------------------------------------------|-----------|---|

|   | 3.1          | Introduction                                                            | 49        |   |

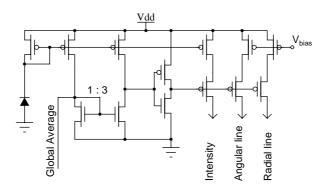

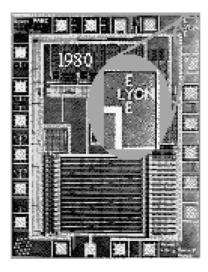

|   | 3.2          | Lyon's eye                                                              | 50        |   |

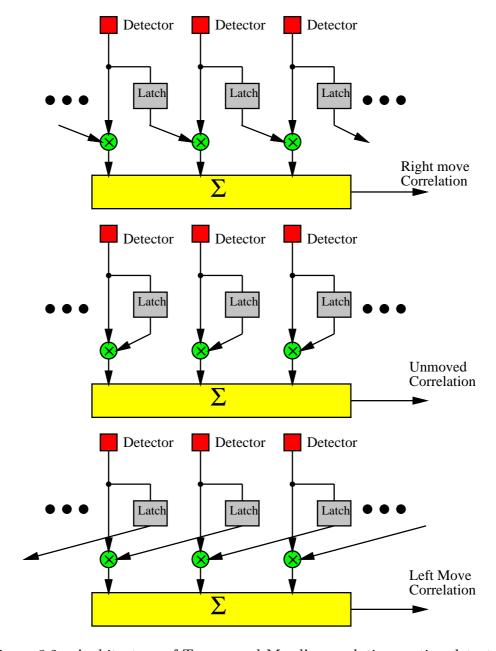

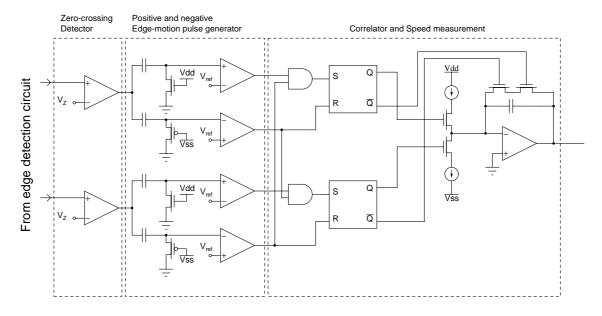

|   | 3.3          | Tanner and Mead's correlating motion detection chip                     | 51        |   |

|   | 3.4          | Tanner and Mead's optic flow motion detection chip                      | 53        |   |

|   | 3.5          | Moore and Koch's multiplicative motion detector                         | 54        |   |

|   | 3.6          | Bair and Koch's motion detection chip                                   | 55        |   |

|   | 3.7          | Delbrück's focusing chip                                                | 56        |   |

|   | 3.8          | Delbrück's velocity tuned motion sensor                                 | 57        |   |

|   | 3.9          | Meitzler et al.'s sampled-data motion chip                              | 59        |   |

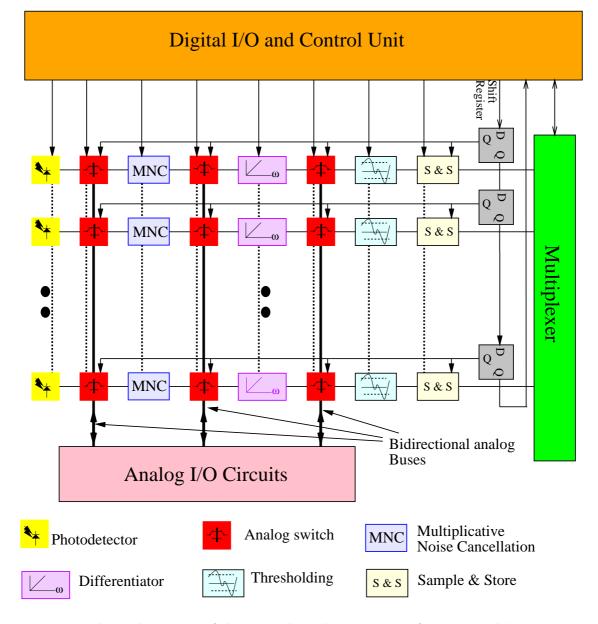

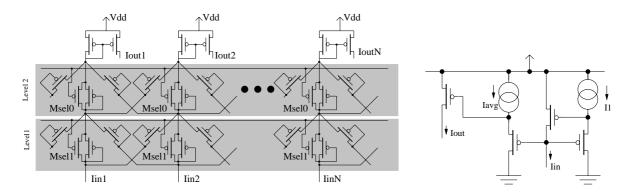

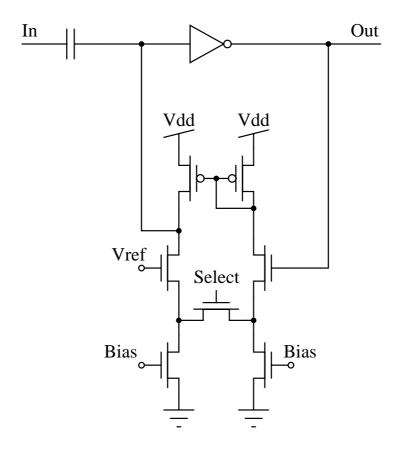

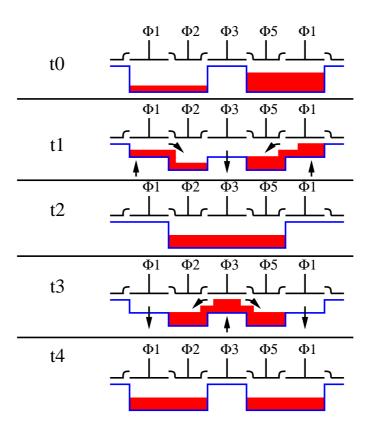

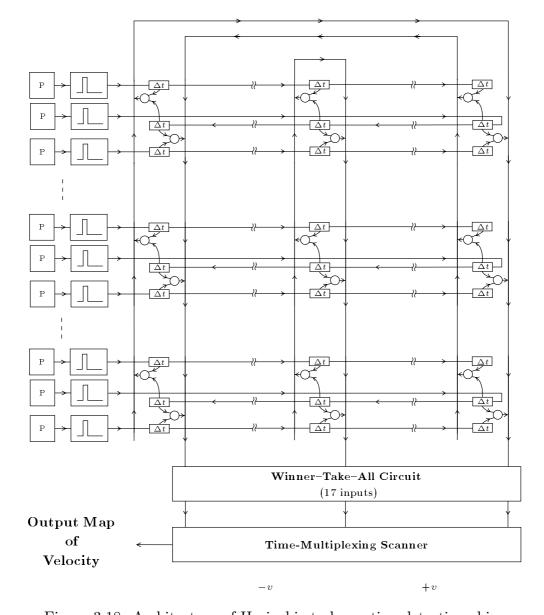

|   | 3.10         | Moini et al.'s insect vision-based motion detection chip                | 60        |   |

|   | 3.11         | r                                                                       | 62        |   |

|   | 3.12         | Dron's multi-scale veto CCD motion sensor                               | 65        |   |

|   |              | Horiuchi et al.'s delay line-based motion detection chip                | 66        |   |

|   | 3.14         | Chong et al.'s change detector                                          | 68        |   |

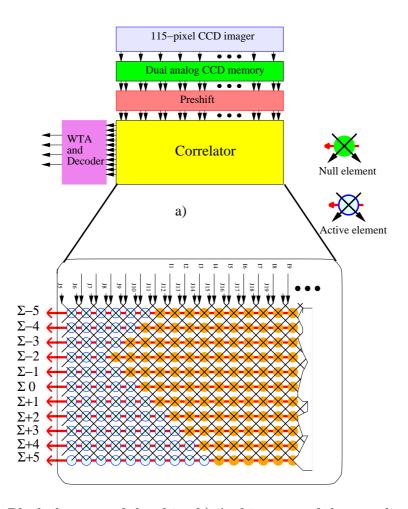

|   | 3.15         | Gottardi and Yang's CCD/CMOS motion sensor                              | 69        |   |

|   |              | Kramer et al.'s velocity sensor                                         | 70        |   |

|   |              | Indiveri et al.'s time-to-crash sensor                                  | 72        |   |

|   | 3.18         | Indiveri et al.'s direction-of-heading detector                         | 74        |   |

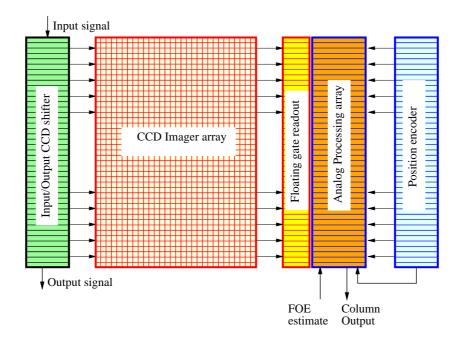

|   |              | McQuirk's CCD focus of expansion estimation chip                        | 75        |   |

|   |              | Gruss et al.'s range finder                                             | 76        |   |

|   |              | Sarpeshkar et al.'s pulse mode motion detector                          | 77        |   |

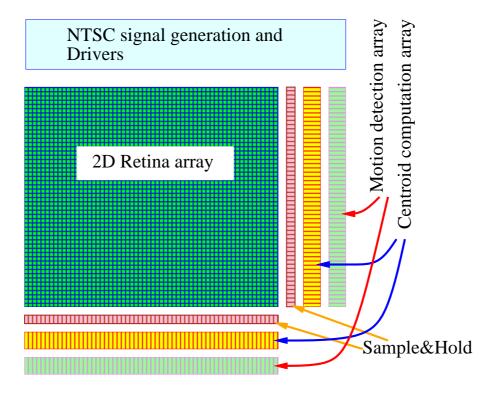

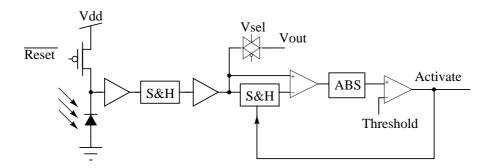

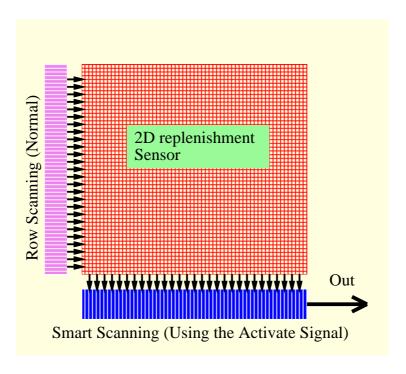

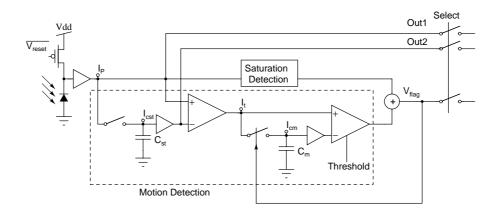

|   |              | Meitzler et al.'s 2D position and motion detection chip                 | 79        |   |

|   |              | Aizawa et al.'s Image Sensor with Compression                           | 80        |   |

|   |              | Hamamoto et al.'s Image Sensor With Motion Adaptive Storage Time        | 82        |   |

|   |              | Simoni et al.'s Optical Sensor and Analog Memory Chip with Change Detec |           | 3 |

|   |              | Espejo et al.'s Smart Pixel CNN                                         |           |   |

|   |              | Moini et al.'s Shunting Inhibition Vision Chip                          | 85        |   |

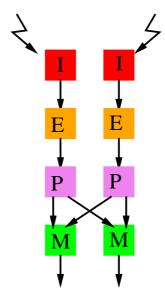

|   |              | Etienne-Cummings et al.'s Motion Detector Chip                          | 86        |   |

|   | 3.29         | CSEM's Motion Detector Chip for Pointing Devices                        | 88        |   |

| 4 | Chi          | ps for Vision                                                           | 90        |   |

| • | 4.1          | Introduction                                                            | 90        |   |

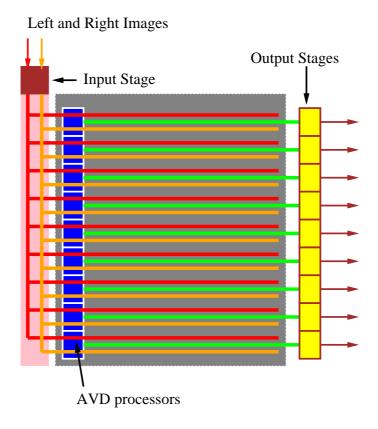

|   | 4.2          | Hakkaranien & Lee's AVD CCD Chip for Stereo Vision                      | 91        |   |

|   | 4.3          | Erten's CMOS Chip for Stereo Correspondence                             | 93        |   |

|   | 1.0          | Enter a Chief of Stores Correspondence                                  | 50        |   |

| 5 | Opt          | ical Neuro Chips                                                        | <b>95</b> |   |

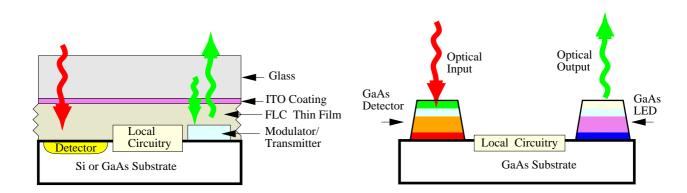

|   | 5.1          | Mitsubishi Electric's Optical neurochip and retina                      | 95        |   |

|   | 5.2          | Yu et al.'s optical neurochip                                           | 97        |   |

| • | A            | San Direct Communication                                                | 00        |   |

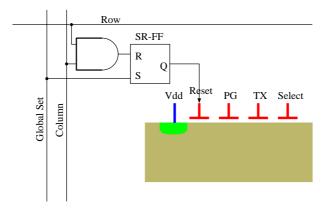

| 3 |              | ive Pixel Sensors Introduction                                          | 99        |   |

|   | 6.1          | Introduction                                                            | 99        |   |

|   | 6.2          | JPL's active pixel sensors                                              |           |   |

|   | 6.3          | Technion's Adaptive Sensitivity CCD Imager                              |           |   |

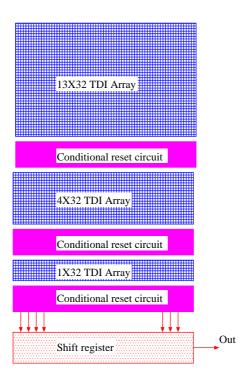

|   | $6.4 \\ 6.5$ | Technion's TDI CCD sensor                                               |           |   |

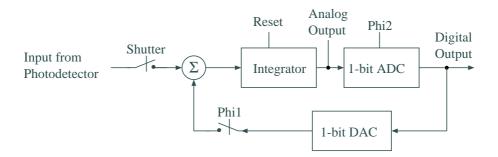

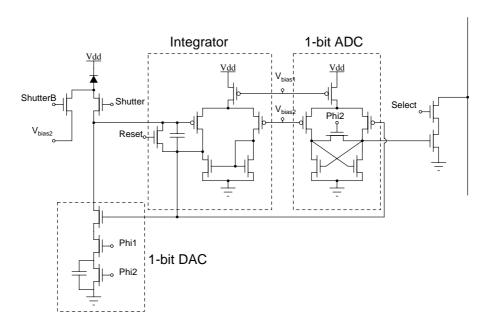

|   | 0.0          | TOWIEL EL AL, S DIXELLEVEL ALDO SELISOL                                 | 104       |   |

The Univ. of Adelaide CONTENTS

| 7            | Pri | nciples | s & Building Blocks                                   | 104 |

|--------------|-----|---------|-------------------------------------------------------|-----|

|              | 7.1 | Introd  | luction                                               | 105 |

|              | 7.2 |         | transduction, the Doorway to Vision Chips             |     |

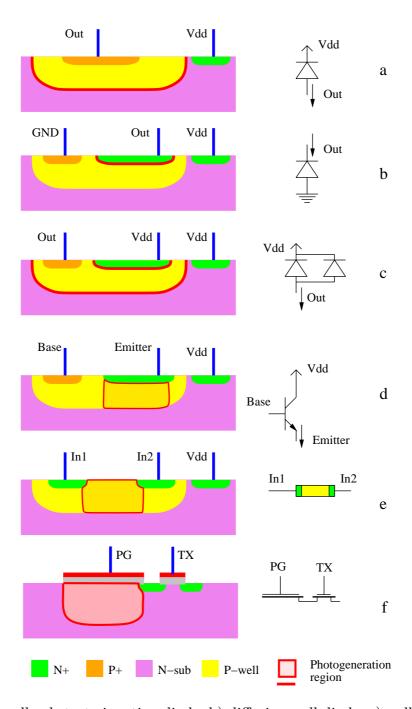

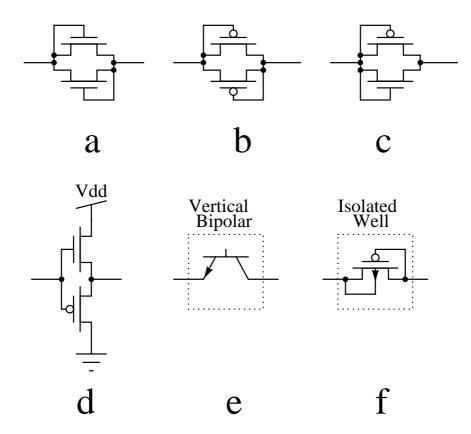

|              |     | 7.2.1   | Photodetector Elements                                |     |

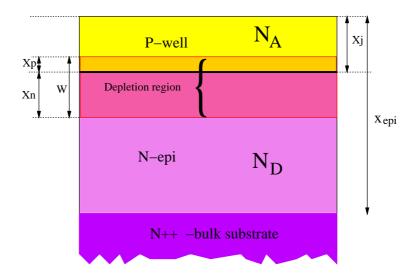

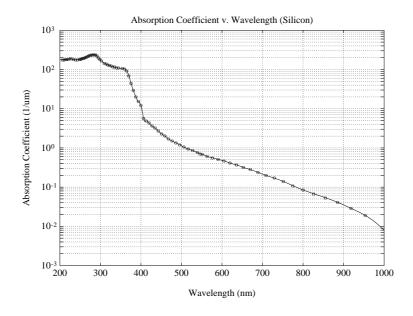

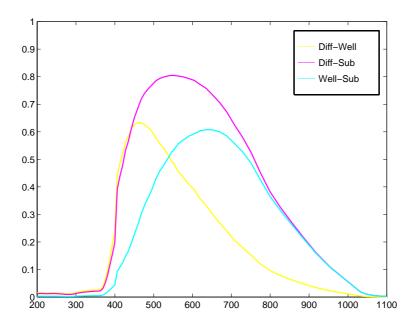

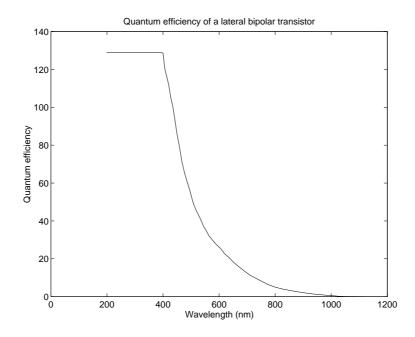

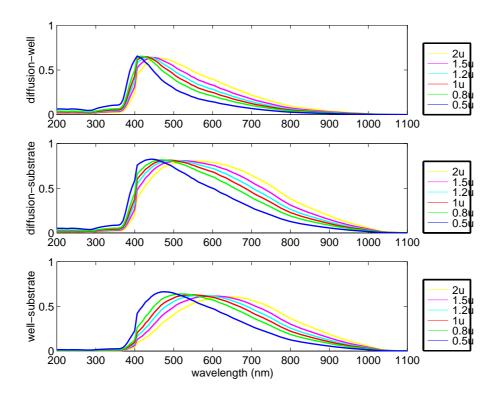

|              |     | 7.2.2   | Quantum Efficiency of a Vertical Junction Diode       |     |

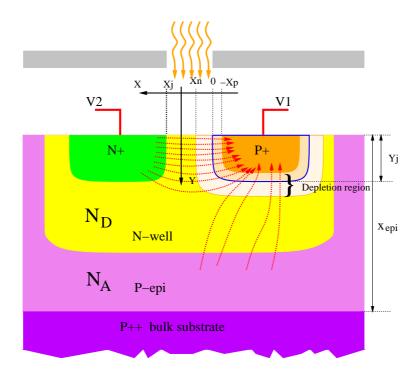

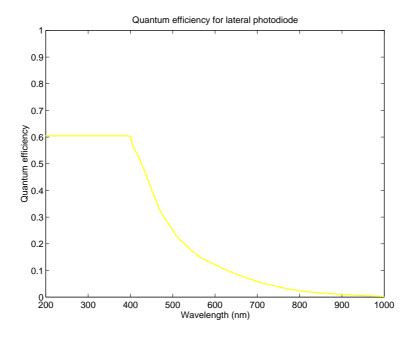

|              |     | 7.2.3   | Quantum Efficiency of a Lateral Junction Diode        |     |

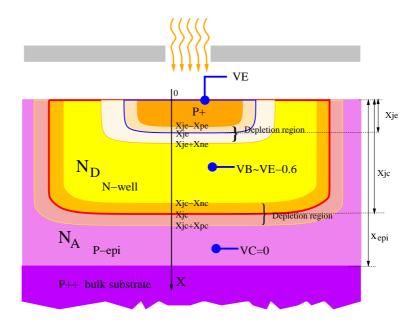

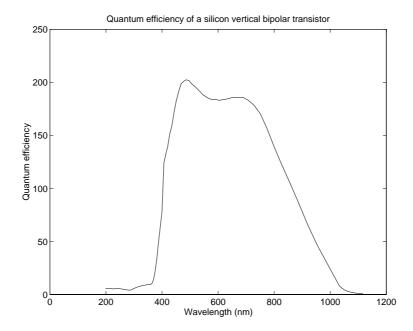

|              |     | 7.2.4   | Quantum Efficiency of a Vertical Bipolar transistor   |     |

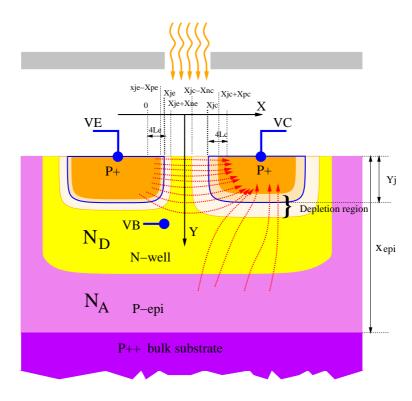

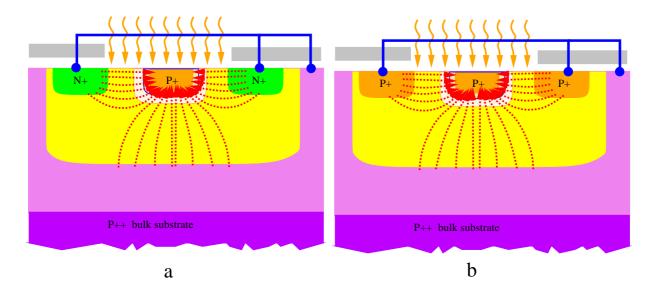

|              |     | 7.2.5   | Quantum Efficiency of a Lateral Bipolar Photodetector |     |

|              |     | 7.2.6   | Mixed structures                                      |     |

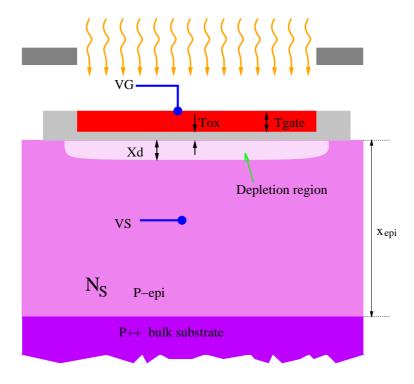

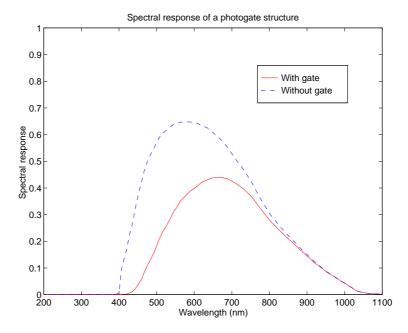

|              |     | 7.2.7   | Quantum Efficiency of a Photogate                     |     |

|              |     | 7.2.8   | The Effect of Scaling on Photodetecting Elements      |     |

|              |     | 7.2.9   | Mismatch in Photodetecting Elements                   |     |

|              | 7.3 |         | ocircuits                                             |     |

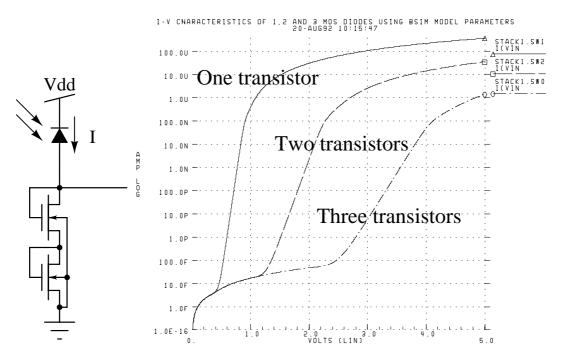

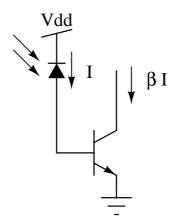

|              | 1.0 | 7.3.1   | Logarithmic Sensor Using MOS Diodes                   |     |

|              |     | 7.3.1   | Photocircuit with Buffer-like Pull-up                 |     |

|              |     | 7.3.2   | -                                                     |     |

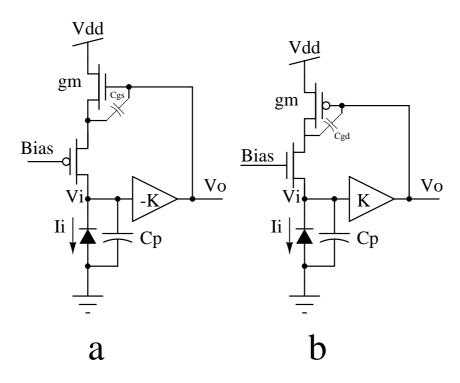

|              |     | 7.3.4   | Photocircuit with Amplifier-like Pull-up              |     |

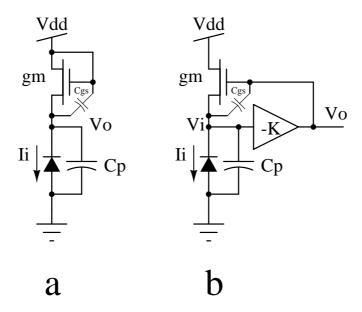

|              |     |         | Buffered Logarithmic Photocircuit                     |     |

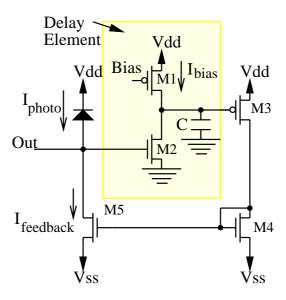

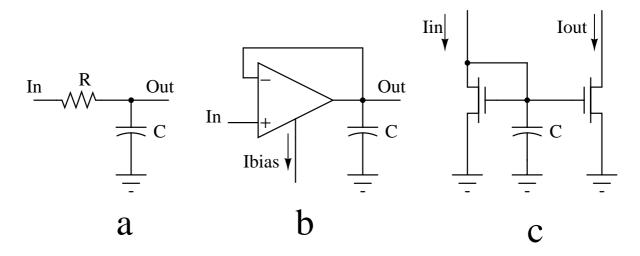

|              |     | 7.3.5   | Delbrück's Adaptive Photocircuit                      |     |

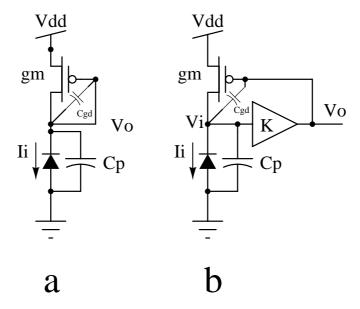

|              |     | 7.3.6   | Cascoded Photocircuits                                |     |

|              |     | 7.3.7   | Current Amplifier Photocircuit                        |     |

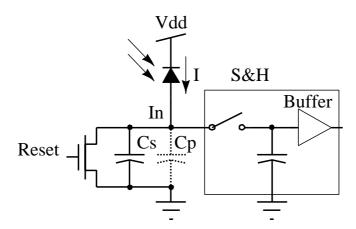

|              | - 4 | 7.3.8   | Integration Based Photocircuits                       |     |

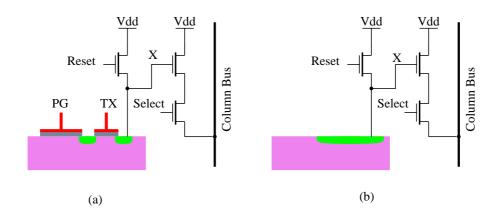

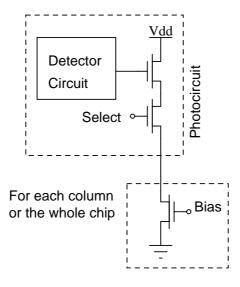

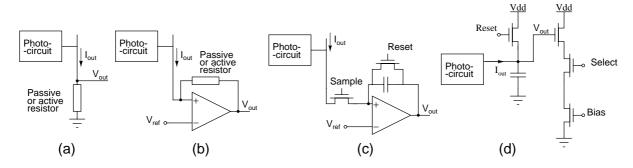

|              | 7.4 |         | its and techniques for active pixel sensors           |     |

|              |     | 7.4.1   | Photocircuits in active pixel sensors                 |     |

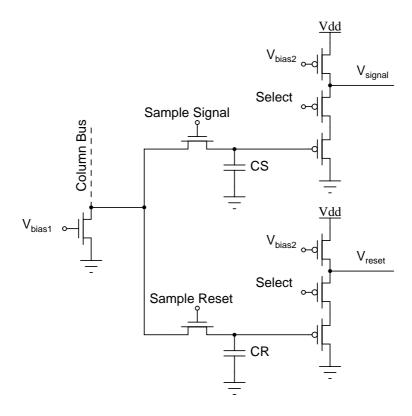

|              |     | 7.4.2   | Correlated double sampling                            |     |

|              | 7.5 |         | al Processing                                         |     |

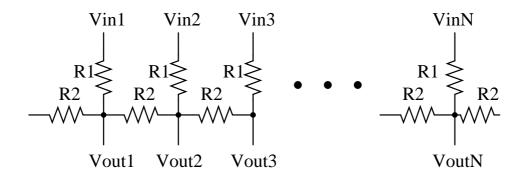

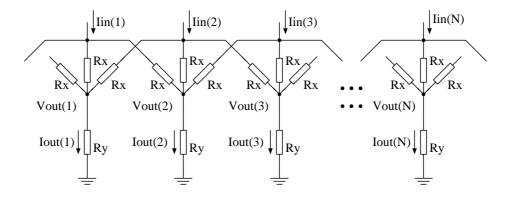

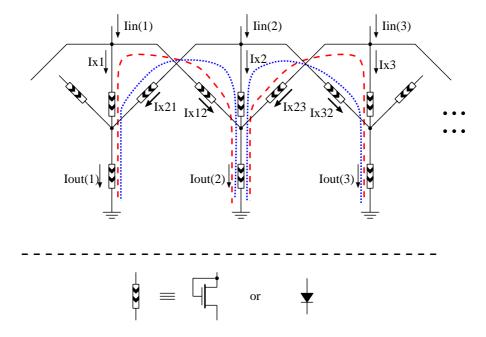

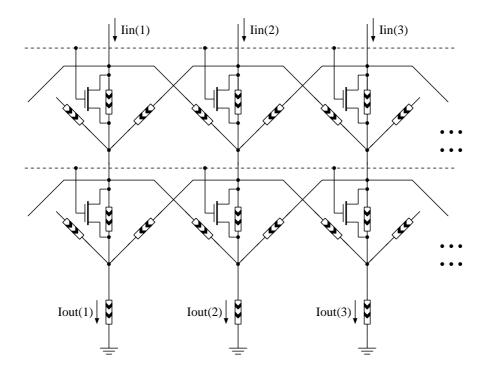

|              |     | 7.5.1   | Linear Resistive networks                             |     |

|              |     | 7.5.2   | Smoothing networks                                    |     |

|              |     | 7.5.3   | Nonlinear Resistive networks                          |     |

|              |     | 7.5.4   | Resistive Circuits                                    |     |

|              |     | 7.5.5   | CCD Circuits for Spatial Processing                   |     |

|              | 7.6 | Spatio  | o-Temporal Processing                                 |     |

|              |     | 7.6.1   | Analog Memory Elements                                |     |

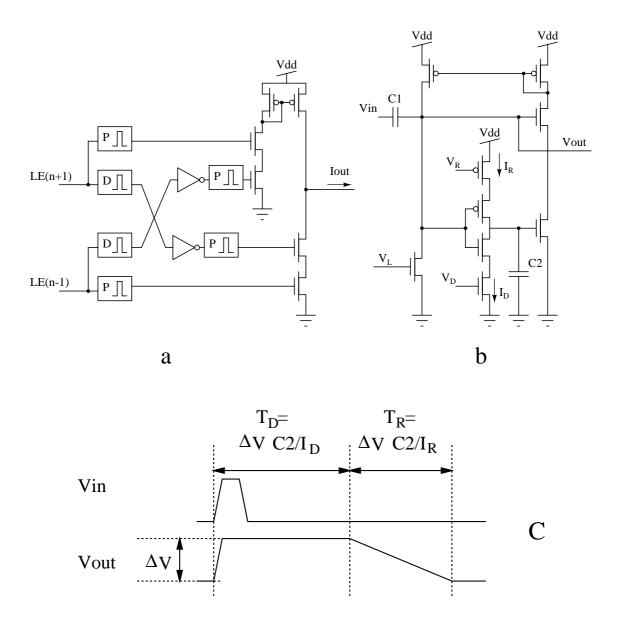

|              |     | 7.6.2   | Continuous Delay Elements                             | 148 |

|              | 7.7 | Adapt   | tation                                                | 149 |

|              |     | 7.7.1   | Light Adaptive Photodetectors                         | 149 |

|              |     | 7.7.2   | Light Adaptive Photocircuits                          | 149 |

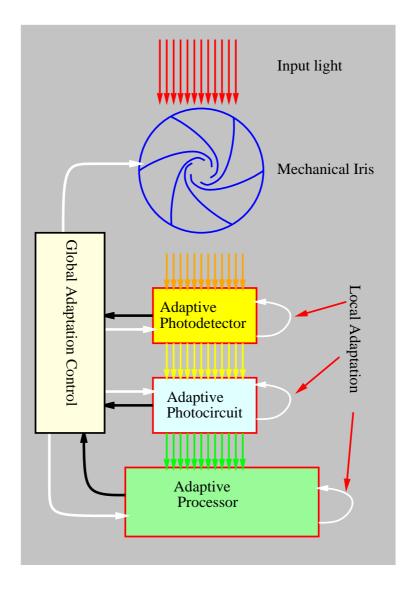

|              |     | 7.7.3   | Light Adaptive Architectures                          | 151 |

|              |     | 7.7.4   | Spatial Adaptation Models                             | 152 |

|              | 7.8 | Practi  | ical issues in designing vision chips                 | 155 |

|              |     | 7.8.1   | Mismatch                                              | 155 |

|              |     | 7.8.2   | Digital noise                                         | 156 |

|              | 7.9 | Testin  | ng vision chips                                       | 157 |

|              |     | 7.9.1   | Design for Testing                                    |     |

|              |     | 7.9.2   | Tests and Measurements                                |     |

|              |     | 7.9.3   | Test conditions                                       |     |

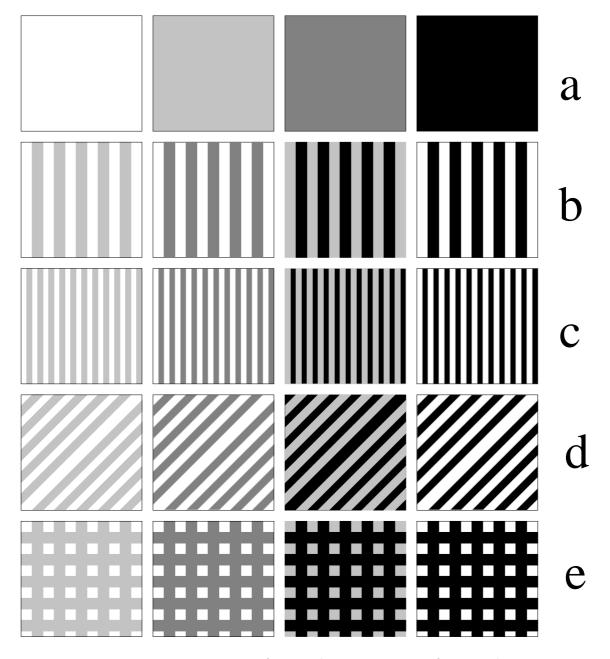

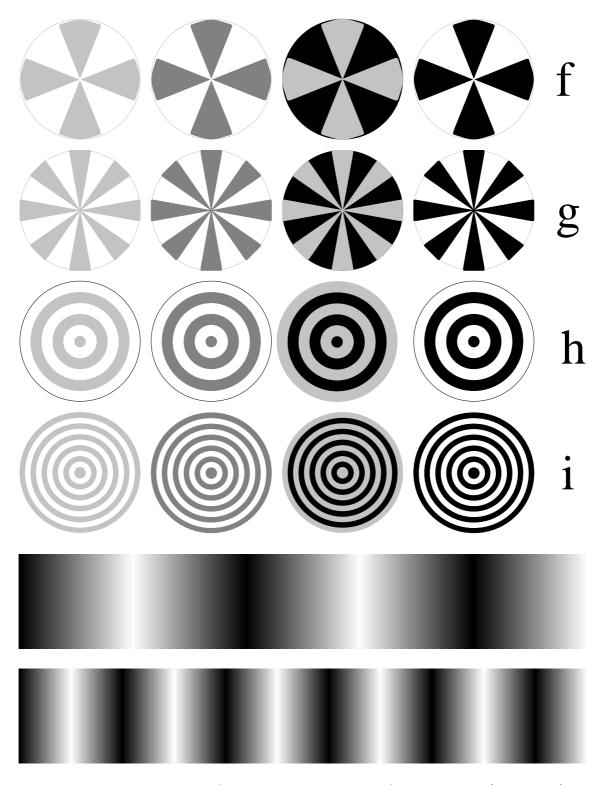

|              |     | 7.9.4   | Steady-state tests                                    |     |

|              |     | 7.9.5   | Spatio-temporal tests                                 |     |

|              |     |         | ~F vompour vozoz                                      | 102 |

| $\mathbf{A}$ | Oth | er res  | ources                                                | 166 |

The Univ. of Adelaide CONTENTS

| Vision Chips or Seeing Silicon | Vision | Chips | $\mathbf{or}$ | Seeing | Silicon |

|--------------------------------|--------|-------|---------------|--------|---------|

|--------------------------------|--------|-------|---------------|--------|---------|

| - 1 |

|-----|

| 4   |

|     |

| В | About this report | 167 |

|---|-------------------|-----|

|   | References        | 168 |

### Chapter 1

### Introduction

Smart vision systems will be an inevitable component of future intelligent systems. Conventional vision systems, based on the system level integration (or even chip level integration) of an imager (usually a CCD) camera and a digital processor, do not have the potential for application in general purpose consumer electronic products. This is simply due to the cost, size, and complexity of these systems. Because of these factors conventional vision systems have mainly been limited to specific industrial and military applications. Vision chips, which include both the photosensors and parallel processing elements (analog or digital), have been under research for more than a decade and illustrate promising capabilities.

### 1.1 Smart sensors

The integration of photodetecting elements and processing circuits on the same chip, for obtaining better performance from sensors, or for making the sensing and processing system more compact, is not a new idea, but the concept of smart sensing, i.e. sensor information processing without redundant and unnecessary data acquisition, and with atsensor-level processing is relatively new. The word "smart-sensors" sometimes has been applied to those sensors which have only tried to integrate the sensors and processing modules, without any regard to the low level interaction that can exist between the sensors and processors. With this meaning in mind, even large systems with a vidicon and a 100kg main frame computer could be called a smart-sensor. The only difference would be the size. Here I would like to use a more fundamental meaning for smart-sensors. "Smart-sensors are those devices in which the sensors and circuits co-exist, and their relationship with each other and with higher-level processing layers goes beyond the meaning of transduction. Smart-sensors are information sensors, not transducers and signal processing elements. Smart sensors are not general purpose devices. Everything in a smart sensor is specificly designed for the application targeted for." With this meaning in mind we exclude any cameraprocessor combination, even if they are integrated on the same chip. However, sensors such as NSIP architecture described in [Aström 93, Forchheimer and Aström 94] and column parallel architecture in [Hamamoto et al. 96a, Hamamoto et al. 96c], although do not integrate the sensors and processors at the pixel level, still possess a tight relationship between the sensors and processors. In fact these architectures suggest that some of the drawbacks of vision chips, such as loss of resolution and fill-factor, may be relieved, while maintaining a semi-parallel processing (in one dimension).

Traditional photodetectors could only output an analog signal, which required further signal conditioning. Still in most imagers the main focus is on the quality of the imaging in terms of noise, resolution, speed, and so on. It is assumed that further signal and image processing stages can acquire the imager output and process it. In contrast, in vision chips the main focus is on the quality of processing. The implementation of a certain algorithm using existing components is given the priority and often some image characteristics, such as resolution, are sacrificed.

### 1.2 Advantages and disadvantages of vision chips

When compared to a vision processing system consisting of a camera and a digital processor, a vision chip provides many system level advantages. These include

- **Speed:** The processing speed achievable using vision chips exceeds that of the camera-processor combination. A main reason is the information transfer bottleneck between the imager and the processor. In vision chips information between various levels of processing is processed and transferred in parallel.

- Large dynamic range: Many vision chips use photodetectors and photocircuits which have a large dynamic range over at least 7 decades of light intensity. Many also have local and global adaptation capabilities which further enhances their dynamic range. Conventional cameras are at best able to perform global automatic gain control.

- Size: Using single chip implementation of vision processing algorithms, very compact systems can be realized. The only parts of the system that may not be scalable are the mechanical parts (like the optical interface).

- Power dissipation: Vision chips often use analog circuits which operate in subthreshold region. There is also no energy spent for transferring information from one level of processing to another level.

- System integration: Vision chips may comprise most modules, such as image acquisition, and low level and high level analog/digital image processing, necessary for designing a vision system. From a system design perspective this is a great advantage over camera-processor option.

Although designing single-chip vision systems is an attractive idea, it faces several limitations:

• Reliability of processing: Vision chips are designed based on the concept that analog VLSI systems with low precision are sufficient for implementing many low level vision algorithms. The precision in analog VLSI systems is affected by many factors, which are not usually controllable. As a result, if the algorithm does not account for these inaccuracies, the processing reliability may be severely affected. Vision chips also use unconventional analog circuits which may not be well characterized and understood.

- **Resolution:** In vision chips each pixel includes a photocircuit<sup>1</sup> which occupies a large proportion of the pixel area. Therefore, vision chips have a low fill-factor and a low resolution. The largest vision chip reported has only 210×230 pixels, for a photocircuit consisting of six transistors only [Andreou and Boahen 94a].

- Difficulty of the design: Vision chips implement a specific algorithm in a limited silicon area. Therefore, often off-the-shelf circuits cannot be used in the implementation. This involves designing many new analog circuits. Vision chips are always full custom designed, and full custom design is known to be time consuming and error-prone.

- **Programming:** None of the vision chips are general purpose. In other words, many vision chips are not programmable to perform different vision tasks. This inflexibility is particularly undesirable during the development of a vision system.

### 1.3 Challenges

Vision chip design is a challenging task. One should consider issues from visual processing algorithms to low level circuit design problems, from phototransduction principles to high-level VLSI architectural issues, from mismatch and digital noise to "readout" techniques, from optics to electronics and optoelectronics, from pure analog to mixed analog/digital to pure digital design problems, from biologically inspired vision models to intuitive models to computational models, . . . .

A vision chip requires photodetecting elements, image acquisition circuits, analog conditioning and processing circuits, digital processing and interfacing, and image readout circuitry all on the same chip. Many of these components, such as low level analog processing elements, should exist in number the same as photodetectors. In most cases these components should interact with at least their nearest neighbors. The area required for implementing the circuits and routing the information across the chip has put upper bounds on the realization of reliably functional and high resolution vision chips, and in most implementations resolution or functionality has been sacrificed for the other. The design of vision chips can obviously benefit from the high level integration in current VLSI processes, where more than 10 million transistors can be integrated on a single chip. Unfortunately, advanced processes for high level integration are usually tuned and characterized for leading edge digital processors and DRAMs, suffering from sub-micron effects, such as short channel effects, hot-carrier effects, band-to-band tunneling, gateoxide direct tunneling, gate induced drain leakage (GIDL), drain induced barrier lowering (DIBL), and threshold voltage control [Fienga et al. 94]. Many available processes, on the other hand, do not have any specific photodetecting element, and are not well tuned for analog circuit design. Device mismatch has also severely affected the analog circuit design community, and almost no fabrication processes have been carefully characterized and modeled to account for mismatch.

Design of vision chips has also been affected by the lack of VLSI friendly computer vision algorithms. Most current computational computer vision algorithms are very complex and are even hardly implementable using powerful workstations to run in real time.

<sup>&</sup>lt;sup>1</sup>I have adopted the term "photocircuit" because of its clear and sharp reference to a circuitry which processes the photocurrent or photovoltage. Other terms, such as "photoreceptor", have been interchangeably used both for single photodetectors and the circuitry used for processing photocurrents, and in a context full of these references become confusing.

Many computer vision algorithms are still not reliable enough for application in general uncontrolled environments. Biologically inspired algorithms, on the other hand, rely on the fact that many creatures have developed very efficient visual system. These algorithms, however, are not mature enough and suffer from excessive simplification caused by insufficient understanding of animals visual system.

Despite these facts, the design of single chip VLSI vision sensors, or smart vision sensors is increasingly progressing and many vision chips based on biological or computational algorithms have been developed in the past few years. The complexity of vision chips has also significantly increased, and 2D vision chips with more than 48,000 detectors and processing elements have been designed [Andreou and Boahen 94b].

### 1.4 Technology

Different technologies offer advantages and disadvantages for the design of vision chips. The dominant technologies available to date are CMOS, BiCMOS, CCD, and GaAs (MESFET and HEMT). CMOS has been exhaustively used in many designs. The additional bipolar transistor in BiCMOS processes, though advantageous in achieving better matching properties and higher speeds, is not easily justifiable when comparing other factors in the design. While commercial grade CMOS processes are accessible through fabrication brokers, such as MOSIS and CMP, the CCD processes available for prototyping are of a low quality. GaAs processes have been used only to a very limited extent because there are no readily available photodetector structures in such processes, and more importantly, analog circuit design is severely limited by gate leakage in MESFET and HEMT transistors. In the following sections advantages and disadvantages of each process are highlighted.

#### 1.4.1 CMOS

CMOS has been and will remain the dominant technology is almost all VLSI design areas, including vision chips. This is a direct result of the following advantages offered by CMOS processes.

- Mature technology: CMOS processes are well established and continue to become more mature. The powerful trust by leading edge digital memory and processors has led to continuous improvement and down scaling of CMOS processes.

- **Design resources:** Circuit and system design in CMOS is supported by a vast number resources. Many design techniques and design libraries for analog and digital design are available.

- Availability: CMOS processes are now readily available for prototype designs through fabrication brokers, at low prices. This has boosted the design knowledge by real implementations, rather than pure theoretical treatments.

- **Price:** CMOS is the cheapest process available, when compared against other technologies with the same minimum feature size.

The major disadvantages of CMOS technology for implementing vision chips are:

• Analog circuit design: Leading edge processes are not characterized and tuned for analog circuit design.

- **Photodetectors:** The photodetector structures are not characterized in any of the processes. It is the designer's responsibility to assure that the photodetectors function as desired.

- Second order effects: In the scaling process some second order device characteristics, such as subthreshold operation, are usually ignored or paid less attention, and their cancellation is more desired than their improvement.

- **Mismatch:** Mismatch in CMOS devices is relatively high. This is specially hindering the reliability of analog processing in vision chips.

#### 1.4.2 **BiCMOS**

BiCMOS processes provide an additional bipolar device, which has been the workhorse of analog design. The bipolar transistor can be used to increase the speed, reduce the mismatch, and obtain better circuit characteristics when exponential I-V relatinship is required. However, the use of BiCMOS processes has been limited due to its complexity and cost. Also the large area required for each bipolar transistor makes them unattractive for large vision chips.

### 1.4.3 CCD and CMOS/CCD

CCD processes have originally been developed for analog signal processing and imaging devices. Although this may have facilitated the design of vision chips, due to their drawbacks there has been limited success in achieving functional and reliable vision chips. Major drawbacks of CCD and CCD/CMOS with respect to CMOS are:

- Clocking: To perform even simple operations large number of clock phases are required, these clock phases should be distributed to all cells

- **Process optimization:** Special CCD processes do not have optimized CMOS devices and CCD/CMOS processes do not have optimized CCD structures

- Special read and write circuit: For transferring signals between CMOS and CCD parts in a CCD/CMOS circuit special read/write circuits are necessary

- Large area: Occupying large area per cell due to the above items

- **Digital noise:** Massive clock-induced-noise to analog circuits in mixed CCD/CMOS approach

- Power: Power consumption due to large voltage transients required for clocking the gates of CCD structures (large capacitive loads)

Despite these numerous drawbacks, CCDs offer easier solutions for some operations. For example, in a smoothing CCD vision chip the smoothing width can be increased by only leaving the circuit to operate over more clock cycles. In other words, CCDs are capable of iterating a function without demands on additional space.

#### 1.4.4 GaAs MESFET and HEMT

GaAs processes are recognized by their high speed operation for digital and analog circuits. They have also been used in opto-electronic devices. GaAs processes suffer from several problems

- Maturity of technology: The processes are not mature. It was only recently that GaAs processes could achieve high integration (in the order one million transistors).

- Analog design: Analog circuit design has been affected by the schuttky diode at the gate. This diode is in a forward bias direction. For an enhancement mode MESFET this leaves a gate-source voltage range of 0.1 V to 0.6 V.

- Price and availability: GaAs processes are generally expensive and not easily accessible.

- Opto-electronic devices are only available in very specialized processes.

### 1.5 Major groups working on vision chips

- The works of Carver Mead's group in California Institute of Technology, starting with Lyon's optical mouse designed in 1980(See section 3.2), are major contributions to this exotic and fascinating area of VLSI design. The idea of neuromorphic engineering using VLSI technologies was first introduced by Carver Mead and bloomed into several analog VLSI chips appearing in "the Bible of analog VLSI", Analog VLSI and Neural Systems published by Addison-Wesley in 1989 [Mead 89b]. This work is still continuing in the Carver-Lab in Caltech. The research emphasis in this group is on analog VLSI systems. In the past they have designed many chips using analog VLSI based on biological models of vision, cochlea, and other neural systems.

- Koch-Lab again in Caltech, led by Christoph Koch, has focused on modeling biological neural systems and also implementing them in analog VLSI.

Research in the laboratory of Professor Christof Koch focuses on several areas:

- Biophysics of Computation in Single Neurons

- Cortical Circuits Underlying Motion and Visual Attention

- Psychophysics of Attention and Awareness

- The Neuronal Correlate of Visual Awareness and Consciousness

- Neuromorphic Analog VLSI Vision Systems

- Analog VLSI group in Johns Hopkins University led by Professor Andreas Andreou

has had similar interests in analog VLSI systems as the Carver-Lab. Analog VLSI

chips mainly based on biological models have been designed in this lab. Some

system designs in this lab include analog VLSI models of auditory processing, early

vision and silicon retinas, associative memory, adaptive neural networks, and speech

recognition.

- The VLSI group at Laval University is led by Marc Tremblay. The research is principally inspired by computational needs in computer vision. The VLSI projects are focused on the design and development of smart sensors. Some of the research

topics include the MAR-Camera systems, motion detection, and linear arrays for 3-D cameras.

- The Image Processing Group at Linkoping University in Sweden has been developing vision cameras with processing capabilities. The group led by Andres Astrom has developed the commercially available LAPP and MAPP series cameras.

- Adelaide Uni. in Australia has been pursuing the insect vision based motion detector project since 1991. Inspired by the simplicity of the insect visual system, and using a VLSI friendly model for insect vision, the first insect vision chip was designed in 1992. The project led by Abdesselam Bouzerdoum and Kamran Eshraghian is having a rapid growth in number of people and aspects of the design. The work is being funded by strong industrial partners and the federal government of Australia.

- IMEC and IBIDEM consortium, involving several universities in Spain and Italy, have focused on the design of space variant sensors, more specifically the "foveated sensors". The log-polar mapping performed by these sensors is very attractive for applications requiring rotation and scale invariant processing.

- A research group in MIT has concentrated on the implementation of early visual processing using CCD and CMOS technologies. In this set of projects they have targeted vision tasks and algorithms requiring low precision. The reason in selecting CCD as the base technology for the implementation has been stated to be the achievable compact size.

Some of the chips designed as a part of this project include

- CMOS image moment and orientation chip [Standley 91b]

- CCD/CMOS image smoothing and segmentation chip [Keast and Sodini 92]

- CCD image feature extraction chip [Chiang et al. 90, Chiang and Chuang 91]

- CCD/CMOS focus of expansion chip

- CCD multiscale veto motion sensor [Dron 94]

- CCD/CMOS stereo chip

- The Perception System Lab. in ETCA, France is lead by Thierry Bernard. Activiies in the lab are concentrated on various aspects of designing intelligent systems, including vision chips, and in particular programmable artificial retinas.

- The VLSI Systems group in Southern Illinois University at Carbondale is working on VLSI design of vision chips for real-time dynamic tasks encountered in manufacturing and assembly, auto-navigation, and un-manned vehicles and robotics.

- The Hatori-Aizawa Lab. in Tokyo University, has focused on compression sensors and adaptive imagers for on-chip compression and adaptation.

- The VLSI group in Technion, Israel, headed by Ran Ginosar has been developing adaptive sensitivity smart imagers, and techniques for improving the scanning of imagers.

- A group in Mitsubishi Electric has been developing optical neurochips using exotic III-V compound structures. The main focus of the research has been on optical interconnection and neural network architectures.

- The "SYNERGY" Lab. in Arizona State University led by Lex Akers has concentrated on designing vision chips and adaptive smart sensors "camera on chip".

- A group at EPFL, in Switzerland and led by Erric Vittoz are working on analog VLSI systems. They have designed several vision chips. Due to agreements with industrial partners the works remain unreported to public.

- The VLSI group at the University of Sevilla in Spain which is associated with "National Centre of Microelectronics", has been developing vision chips based on cellular neural networks (CNN).

- The Analog Computation Group in University of Florida is headed by John Harris. The work in this group includes analog VLSI circuits for sensory processing, neural networks, and neurobiological models.

### 1.6 How vision chips are presented in this report

The revolutionary ideas implemented on silicon chips, which will be described in the following sections, are blooming and opening the doors for another information processing tool, smart-visual-sensing. This report is a survey of the vision chips that have been designed in the past decade. It tries to give a concise and simple description of each design and draw the reader's attention to the specific idea that a particular vision chip has brought about. For each chip a brief description about the function of the chip is given. Important architectural and circuit level design aspects are also presented. Basic principles of vision algorithms and circuit design will not be described, at least in detail. The reader is expected to have a good knowledge of image processing, and general knowledge on analog and digital VLSI design. Wherever available, some information about the fabricated chips, like cell size, chip size, and process are also provided. In future revisions more information about the performance of each chip will be presented. Of course, as the computer vision community is still faced with the lack of proper benchmarks and criteria for image processing performance at different levels, most of the performance measures will be those related to VLSI, such as speed, power, and contrast sensitivity, rather than computer vision related measures.

There are some links (in the html format of the report) to the relevant home pages of the authors of each work to make the vision-chip community as close together and as informed as possible from each other's work. Some of the documents are also linked to the online postscript format of the articles relevant to that chip, which can be downloaded and printed on a postscript printer.

In this third revision of the vision chips document, I have added many new vision chips, and the report now comprises more than fifty vision chips. The document encompasses seven chapters.

In chapter 2 Spatial Image Processing Vision Chips are presented. This includes chips for edge detection, smoothing, stereo processing, and contrast enhancement (silicon retinas), in addition to chips for finding global features of the image.

Chapter 3 covers *Spatio-Temporal Image Processing Vision Chips*, dominated by motion detection chips. Although motion detection chips intrinsically include spatial processing, the cooperative time-space processing makes them different from other vision chips. There are also a few purely temporal processing implementations.

Chapter 4 presents a few analog VLSI chips for vision processing. These chips do not have on-chip photodetectors, and the image is produced by external imagers. These implementations cannot be regarded as vision chips in any sense. It is rather the processing, and vision related implementations that makes them interesting for this report. They also represent the type of processing that can be performed – still in analog domain – on the output of any vision chip.

In chapter 5 Optical Neuro Chips are described. These chips architecturally belong to the analog VLSI neuro-chips family, with the exception that the medium for signal transmission is chosen to be optical. However, as the optical neuro chips designed so far aim at image processing, they are included in this report. The role of neural networks in many new image processing algorithms can also justify this inclusion.

Chapter 6 describes some of the active pixel sensor (APS) chips. Their relevance to this report is from the fact that in these imagers the attention is focused on the quality of the imaging, while in vision chips the implementation of an algorithm is the main concern. Many of the methods developed for enhancing the performance of APSs can be adopted for vision chips.

And finally, chapter 7, Designing Vision Chips: Principles and Building Blocks, presents general principles, design limitations, design variables, guidelines to be considered in the design of vision chips, and testing procedure. Also various components of vision chips, i.e. photodetector, photocircuits, spatial and temporal processing circuits are presented in more detail.

Appendices describe some information about this report, such as tools used to generate the document, and give reference to other major resources, on-line or off-line, about vision chips.

The Univ. of Adelaide

### Acknowledgments

Creating this report has been a pleasing reward for me. In the first few days after the first public announcement in 1994 I experienced the great encouragement of the VLSI-Vision community. I was given so many fantastic ideas and suggestions in designing this report. I received information about many recent and past works, which helped me make the report more complete than what I had in mind. Since then I have received continuous and unfading support in various ways, by informing me of other vision chips, by correcting my misunderstanding of technical details, and in many other ways.

I would like to thank all those who encouraged me, supported the idea in different ways, and helped me in different ways, in alphabetical order:

- Prof. Kiyoharu Aizawa (Tokyo Uni., Japan)

- Prof. Andreas Andreou (Johns Hopkins Uni., USA)

- Miguel Arias (Laval Uni., Canada)

- Dr. Thierry Bernard (ETCA/CREA/SP, France)

- Dr. Abdesselam Bouzerdoum (Adelaide Uni., Australia)

- Dr. Tobi Delbrück (Synaptics Inc., USA)

- Dr. Bart Dierickx (IMEC, Leuven, Belgium)

- Prof. Lisa Dron (Northeastern Uni., USA)

- Dr. Gamze Erten (IC Tech Inc., USA)

- Dr. Ralph Etienne-Cummings (Southern Illinois Uni, USA)

- Prof. Gerhard Fasol (University of Tokyo, Japan)

- Dr. Robert Forchheimer (Linkoping Uni., Sweden)

- Dr. Eiichi Funatsu (Photonic LSI Technology Group, Mitsubishi Electric Corp., Japan)

- Prof. Ran Ginosar (Technion, Israel)

- Dr. Mats Gykstorp (R&D Manager, Integrated Vision Products AB, Sweden)

- Dr. Takayuki Hamamoto (The Science University of Tokyo, Japan)

- Rainer Hoehler (Darmstadt University of Technology, Germany)

- Dr. Giacomo Indiveri (Caltech, USA)

- Prof. Eberhard Lange (Advanced LSI System Technology Department, Mitsubishi Electric Corporation, Japan)

- Dr. John Lazzaro (Berkeley & Caltech, USA)

- Ms. Shih-Chii Liu (Caltech, USA)

- Luc Le Pape (Universite de Bretagne Occidentale, France)

- Dr. Richard Lyon (Apple Computer, USA)

- Dr. Richard Meitzler (Johns Hopkins Uni., USA)

- Dr. Fernando Pardo (Diseño Electrónico y Circuitos VLSI, Universidad de Valencia, Spain)

- Prof. Robert Pinter (Washington Uni., USA)

- Dr. John Platt (Director of Research, Synaptics Inc., USA)

- Dr. Elisenda Roca (Centro Nacional de Microelectronica (CNM), Spain)

- Prof. Giulio Sandini (DIST University of Genova, Italy)

- Rahul Sarpeshkar (Caltech, USA)

- Dr. Kim Strohbehn (Johns Hopkins Uni., USA)

- Prof. Marek Syrzycki (Simon Fraser Uni., Canada)

- Prof. Marc Tremblay (Laval Uni., Canada)

- Dr. Rudi Wiedemann (President/CEO of Silicon Vision Inc.)

- Robert Wodnicki (McGill Uni., Canada)

Alireza Moini

### Chapter 2

# Spatial Image Processing Vision Chips

#### 2.1 Introduction

This chapter describes vision chips that implement only a spatial image processing function, from simple local smoothing operations to more complicated and global object orientation detection. Several different categories can be easily recognized among these vision chips.

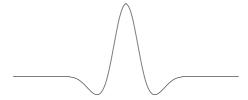

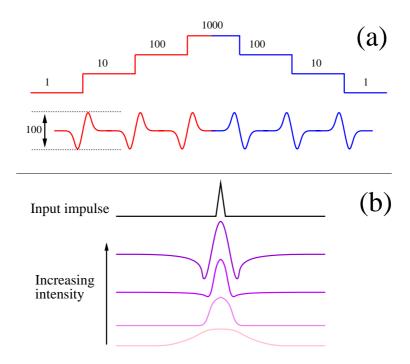

A majority of spatial image processing chips, which have been dubbed *silicon retinas*, are based on models of the vertebrate retina. Some of the general characteristics of the vertebrate retina, which have been given considerable attention, are the adaptation to local and global light intensity, and edge enhancement. Various models have been proposed for the form and function of the retina, such as Laplacian of Gaussian (LOG), Difference of Gaussian (DOG), a direct derivate of the biharmonic equation, and linear and multiplicative lateral inhibition. Not surprisingly, the form of the kernel convolution function in all of these models has a mexican-hat shape shown in Figure 2.1, though the underlying mathematical or biological theories may be quite different<sup>1</sup>. Which one of these models can best approximate the function of the retina is still subject to more experience with these models and the retina itself.

Figure 2.1: The mexican hat. A generic kernel with different explanations and models.

The Gaussian filtering plays an important role in most of the models used in implementing silicon retinas. The smoothing operation performed at any stage, and specially at the front-end, may help in reducing the noise. In some silicon retinas Gaussian filtering is followed by a subtraction or division stage, to enhance the edges and make the

<sup>&</sup>lt;sup>1</sup>We should remember that all these models have been obtained under various assumption to regularize the specific problem or to simplify the model

image invariant to the local intensity, at a neighborhood determined by the characteristics of the Gaussian filtering. In many silicon retinas a simple 1-D or 2-D resistive network serves as the basic element for approximating the Gaussian smoothing function. Only one implementation utilizes a more accurate approximation to the Gaussian filtering [Kobayashi et al. 95b].

Another group of spatial processing vision chips target more global features of the image, such as the *object position and orientation chip* [Standley 91b] or the *centroid computation chip* [Dewerth 92].

Foveated sensors constitute another group of spatial vision chips. In these sensors the physical size and placement of the photodetectors form a log-polar mapping on the image. Log-polar mapping is rotation and scale invariant, with a high resolution in the centre, and logarithmically decreasing resolution off the centre.

#### 2.2 Mahowald and Mead's silicon retina

Mahowald's silicon retina chip is among the first vision chips which implemented a biological facet of vision on silicon [Mahowald 94a, Mead 89b]. The computation performed by Mahowald's silicon retina is based on models of computation in distal layers of the vertebrate retina, which include the cones, the horizontal cells, and the bipolar cells. The cones are the light detectors. The horizontal cells average the outputs of the cones spatially and temporally. Bipolar cells detect the difference between the averaged output of the horizontal cells and the input.

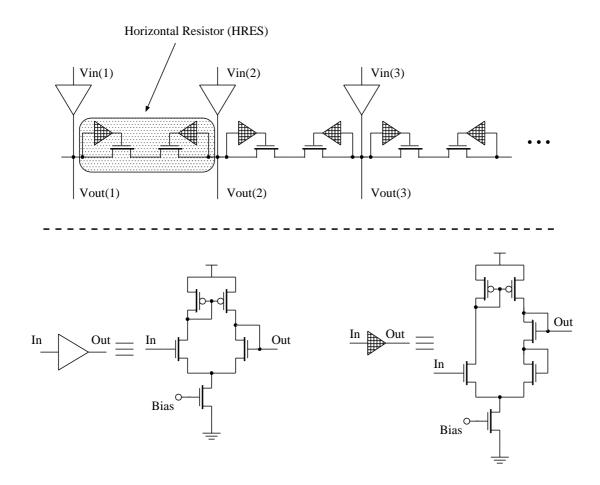

In this silicon retina the cones have been implemented using parasitic phototransistors and MOS-diode logarithmic current to voltage converters. Averaging is performed using a hexagonal network of active resistors as shown in Figure 2.2. The resistors are implemented using the horizontal resistor described in [Mead 89b]. The shape of the smoothing operation performed by the resistive network is similar to the charge distribution in semi-conductors, and is an exponential function. The smoothing factor depends on the value of the resistors (or diffusion constant in semi-conductors).

This silicon retina is in fact a simple implementation of other silicon retinas, which will be described later and are referenced in [Andreou and Boahen 94b, Bair and Koch 91b]. In those implementations two separate smoothing networks with different smoothing constants are used. The corresponding outputs of the two smoothing networks are then compared using a differentiating function, such as division or subtraction. In Mahowald's silicon retina only one smoothing network has been implemented. Yet it demonstrates many similarities between the signals obtained from a real retina (of a mud puppy) with those obtained from the silicon retina.

Figure 2.2: Architecture of Mahowald's silicon retina.

### 2.3 Mead's adaptive retina

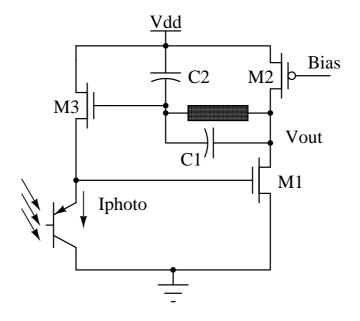

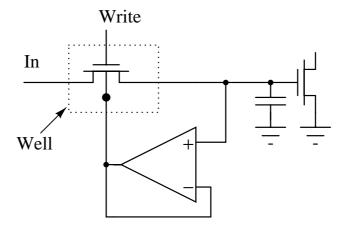

Mead's adaptive retina [Mead 89a] is an enhanced implementation of Mahowald's silicon retina described in Section 2.2. The chip uses floating gate MOSFETs (FGMOS) as a feedback element used for correcting the problem of offset and mismatch between transistors.

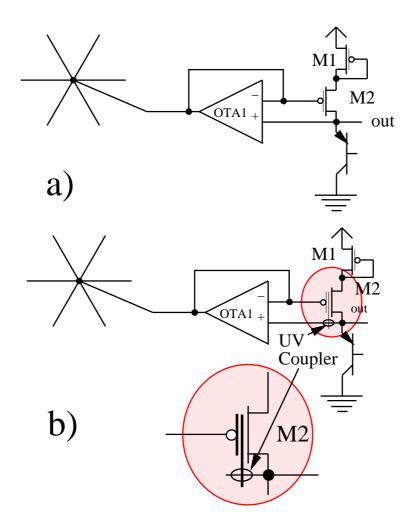

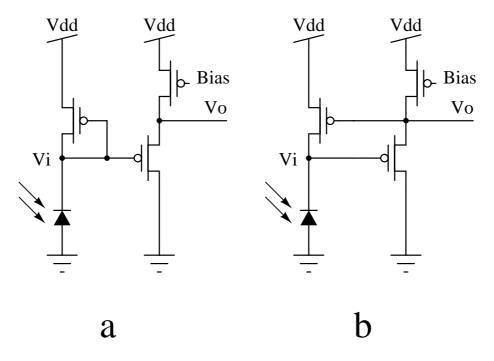

Figure 2.3 shows two circuits with and without the FGMOS transistor. The retina chip using the circuit in Figure 2.3-a had demonstrated a very sensitive operation in which the output voltage of many pixels were stuck to Vdd or Gnd supply voltages under uniform illumination. The reason is that a small offset in OTA1 is amplified by the inverting amplifier and the output will saturate to one of the supply rails.

In order to mitigate this problem a feedback loop has been constructed to compensate for the effect of mismatch by changing the effective threshold voltage of transistor M2. This has been realized by the UV activated coupler, which is a simple poly1-poly2 structure. When the poly1-poly2 structure is exposed to the UV light, the feedback loop is closed and the floating gate sits at a voltage which holds the output voltage, at a level which depends on the input current (if the coupler becomes short circuit, the pull up circuit will be the simple two stacked MOS diode).

Figure 2.3: a) the circuit without FGMOS, b) the circuit with FGMOS.

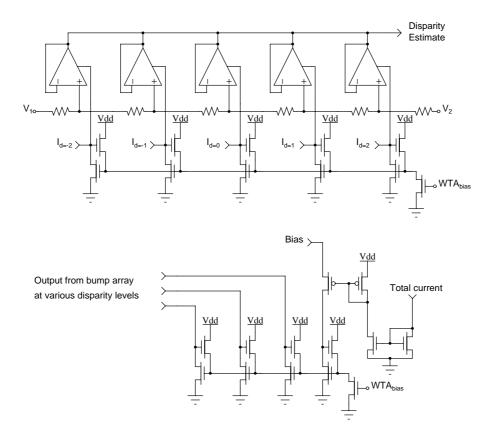

### 2.4 Mahowald and Delbrück's stereo matching chips

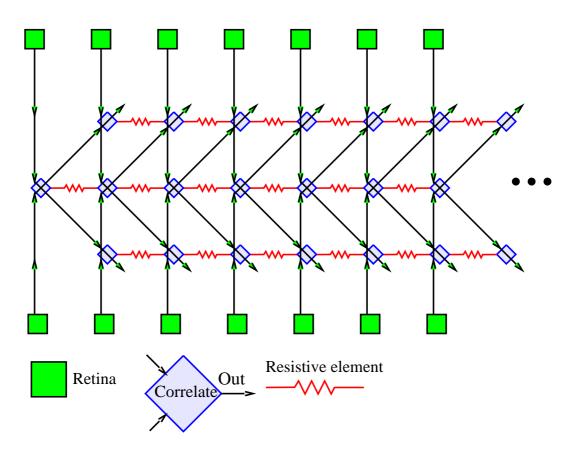

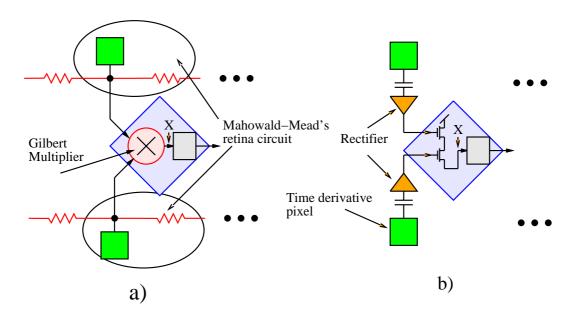

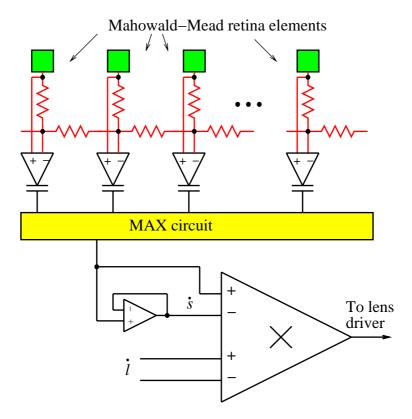

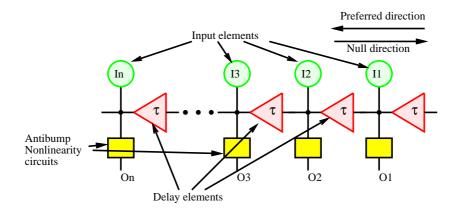

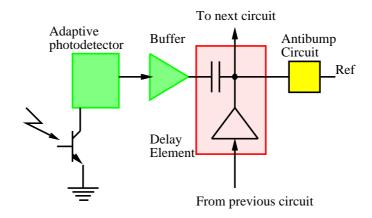

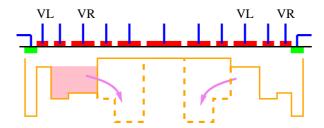

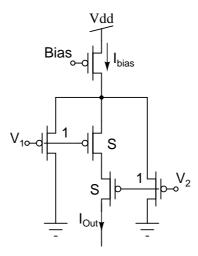

In [Mahowald and Delbrück 89] Mahowald and Delbrück present two stereo matching chips which use static and dynamic features of image. Both chips use Marr/Poggio's algorithm for stereo matching of two right and left image planes [Marr and Poggio 76], and compute disparities on nine disparity planes. The chip architecture is shown in Figure 2.4, which illustrates only three disparity planes. In the first chip, retina elements are a 1D version of the 2D Mahowald-Mead's retina described in Section 2.2 [Mahowald 94a]. The outputs of the two right and left retinas are multiplied together using a four-quadrant Gilbert multiplier and provide input for the correlator. In the second chip the retina elements are not connected together and are based on the time-derivative pixel circuit, which is capacitively coupled to a rectifier. The block diagrams of the correlator input circuitry in both chips are shown in Figure 2.5.

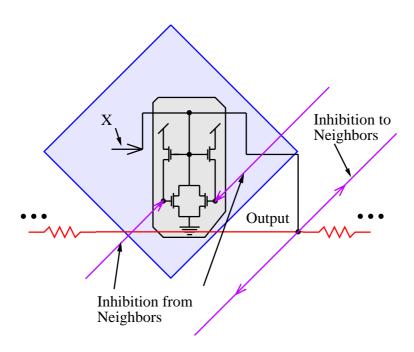

The correlation circuitry after node "X" in the correlator box is similar in both chips and is shown in Figure 2.6. The final output of the chips are the voltages at the *Output* nodes of the correlator circuits.

The chips have 40 pixels in a  $2\mu m$  CMOS process. Experimental results are provided in [Mahowald and Delbrück 89].

Figure 2.4: Architecture of Mahowald-Delbrück's stereo matching chip. Excitation in a disparity plane is done by the resistive elements. The inhibitory connections from neighboring disparity planes are not shown.

Figure 2.5: Schematic diagram of correlator input for a) the static input image chip, and b) the dynamic input image chip.

Figure 2.6: Simplified circuit of the correlator.

#### 2.5 Bernard et al.'s Boolean artificial retina

Bernard et al. describe an artificial retina in [Bernard et al. 93a]. The main difference between this retina and other implementations is that the image is digitized at the very first stage, and processing is performed by Boolean operators acting at the pixel level. The main advantage of this digital retina over analog approaches is its programmability for performing different tasks with the same hardware.

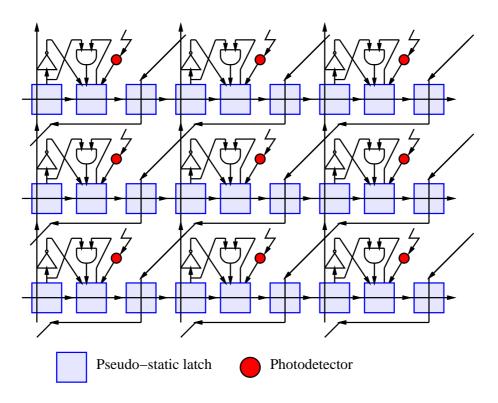

Photodetection has been realized using photocurrent integration followed by thresholding. Therefore the signal becomes digital right at the detector level. The rest of the implementation concerns the design of digital Boolean processors in an architecture called neighborhood combinatorial processing (NCP). A partial set of implemented Boolean operations is shift-up, shift-down&left, shift-right, circular permutation and inversion, copy, inverting copy, conjunction, conjunction and inversion, writing the photodiode, and reading the photodiode. These instructions are coded into a pseudo-static digital circuit, which uses six control signals. The architecture of Bernard's digital retina indicating its pixel level interaction is illustrated in Figure 2.7. Further details about the design of this digital circuit can be found in [Bernard et al. 93a].

By combining simple instructions more complicated operations can be performed. Operations such as edge detection, motion detection, and halftoning have been successfully demonstrated using the chip.

Several versions of the chip have been designed and fabricated. One of them occupies an area of  $50mm^2$  and contains a  $65\times76$  array of photodetectors and Boolean processors, using a  $2\mu$ m CMOS process.

Figure 2.7: Architecture of Bernard et al.'s digital retina.

### 2.6 Andreou and Boahen's silicon retina

This silicon retina is an implementation of the outer-plexiform of retinal processing layers [Andreou and Boahen 94b, Boahen and Andreou 92]. The design has a distinctive feature that separates it from all other silicon retinas. The implementation uses a very compact circuit, which has enabled the realization of a  $210 \times 230$  array of image sensors and processing elements with about 590,000 transistors, which is the largest among all reported vision chips.

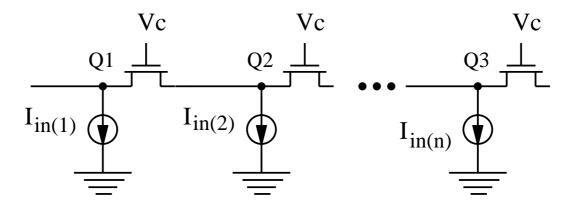

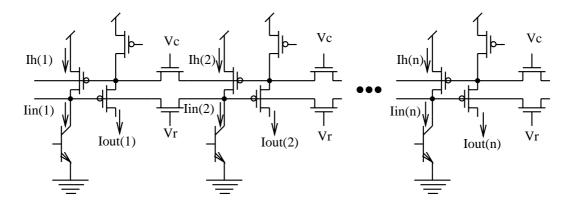

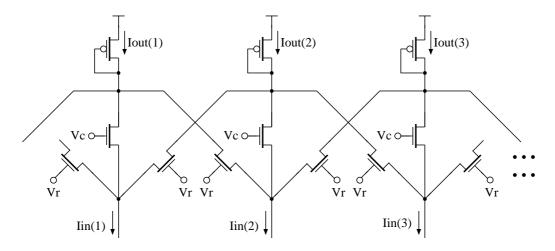

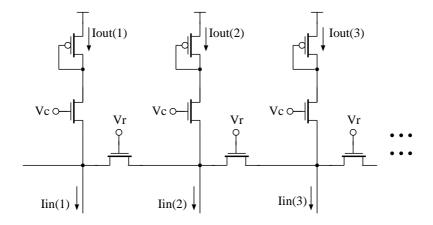

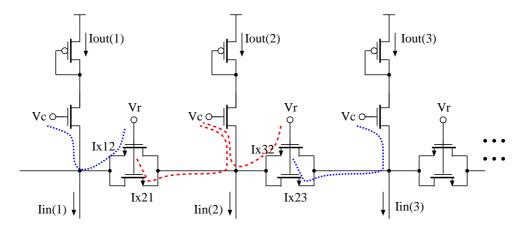

This silicon retina uses a diffusive smoothing network shown in Figure 2.8 [Andreou and Boahen 94b] The function of this one-dimensional network can be written as

$$\frac{dQ_n}{dt} = D\left([Q_{(n+1)} - Q_{(n)}] - [Q_{(n)} - Q_{(n-1)}]\right)$$

dQn/dt is the current supplied by the network to node n, and D is the diffusion constant of the network, which depends on the transistor parameters, and the voltage  $V_C$ .

Andreou and Boahen have encapsulated the model of the retina in a neat and small circuit illustrated in Figure 2.9. This circuit includes two layers of the diffusive network. The upper layer corresponds to horizontal cells in retina and the lower layer to cones. Horizontal N-channel transistors model chemical synapses.

The function of the network can be approximated by the biharmonic equation

$$gh\nabla^2\nabla^2 I_h(x,y) + I_h(x,y) = I(x_i, y_i)$$

$$I_{out}(x_i, y_i) = \nabla^2 I_h(x_i, y_i)$$

where g and h are proportional to the diffusivity of the upper and lower smoothing layers, respectively. More details about the function of the circuit can be found in relevant references [Andreou and Boahen 94b, Boahen and Andreou 92].

Several versions of the 2D chip have been implemented using the circuit shown in Figure 2.8. All the 2D chips use a hexagonal network with six neighborhood connection. The largest chip occupies an area of  $9.5\times9.3$ , in a  $1.2\mu\mathrm{m}$  CMOS process with two layers of metal and poly. A cell size of about  $39.6\mu\mathrm{m}\times43.8\mu\mathrm{m}$  has been achieved for this implementation. Under typical conditions the chip dissipates 50mW.

Figure 2.8: The diffusive network used in Andreou-Boahen's silicon retina.

Figure 2.9: Schematic of the 1D silicon retinal modeling the outer-plexiform of retinal processing.

### 2.7 Kobayashi et al.'s image Gaussian filter

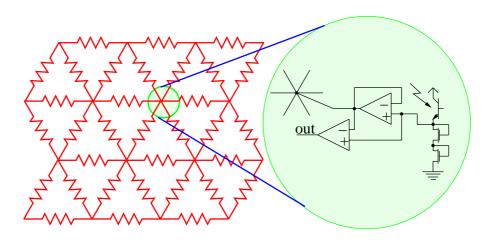

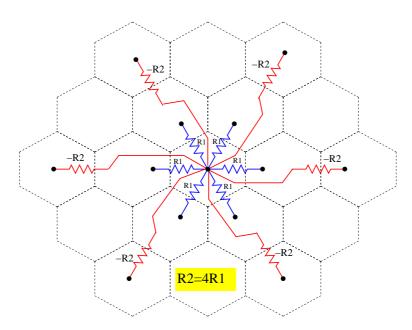

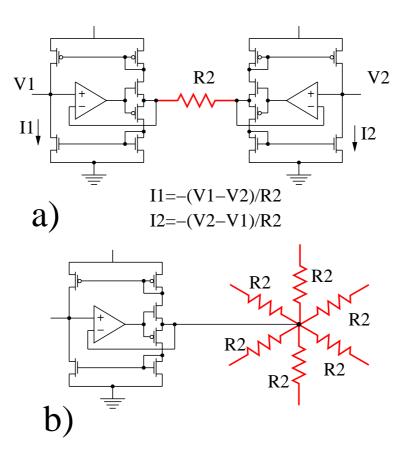

The spatial image Gaussian filter designed by Kobayashi et al. [Kobayashi et al. 95b] uses a hexagonal resistive network. It uses negative resistors implemented using negative impedance converters (NIC) to obtain a better approximation to the Gaussian function, than that obtained using simple resistive networks (an exponentially decaying function similar to charge distribution in bulk semiconductors). The 2D resistor connection is shown in Figure 2.10. In order to get the desired Gaussian characteristic, negative resistances are connected to the second-nearest-neighbors, with four times the value of resistors connecting first-nearest-neighbors. The value "4" has been derived from the discretization of the error energy function, E, for optimizing the fitting function U added with a penalty term, described by

$$E = \sum_{i} (U - V)^{2} + \lambda \int \left(\frac{d^{2}U}{dx^{2}}\right)^{2} dx$$

where the first term is the mean square error between the fitting function U and the input V, and the second term is the penalty term. By discretizing this equation and finding its minimum, a relation between the fitting function and the input can be found.

$$0 = (U_i - V_i) + \lambda(6U_i - 4(U_{i-1} + U_{i+1}) + (U_{i-2} + U_{i+2}))$$

The circuit in Figure 2.11 has been used in the implementation of the NIC elements.

The chip has a  $45\times40$  array of photodetectors and resistive grid on a  $7.9\times9.2$ mm chip using a  $2\mu$ m CMOS process.

Figure 2.10: Kobayashi et al.'s resistive network using negative impedance converters for implementing a Gaussian filter.

Figure 2.11: Negative impedance converter (NIC) used in Kobayashi et al.'s image Gaussian filter. a) obtaining a negative impedance using a resistor and two NIC circuits. b) the usage of the NIC circuit in the chip. One NIC has been used for six resistors.

### 2.8 PASIC sensor from Linköping University

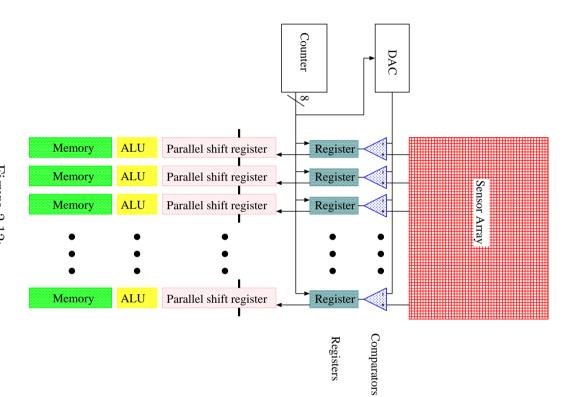

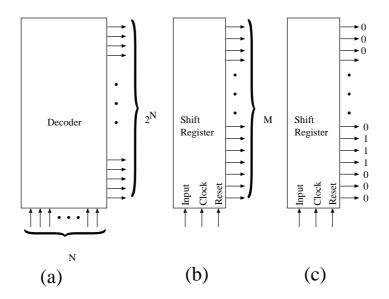

The "Processor ADC and Sensor Integrated Circuit" (PASIC) as the name suggests consists of a sensor array, A/D converters, and processors [Chen et al. 90b, Chen et al. 90a, Chen et al. 90c]. Each column has its own ADC and processor. The architecture of PASIC is shown in Figure 2.12.

A/D conversion is performed in parallel for each selected row. The counter starts from zero and counts up. Whenever the voltage from DAC reaches output voltage of a cell, the counter value is stored in the associated register.

The processing elements consist of three parts, one bi-directional parallel shift register, one ALU, and a memory. These modules communicate to each other through a 1-bit bus. Variaous operation between these modules occur on single bits at a time. Therefore each instruction requires several clock cycles to complete.

Using this bit-serial processor approach several simple image processing operations, such as binary image dilation and erosion, and more complicated operations, such as convolution and histogram collection, have been implemented.

The sensor array in PASIC has  $128 \times 128$  photodetectors. The chip occupies an area of about  $9 \text{mm} \times 11 \text{mm}$ .

### 2.9 MAPP2200 sensor from IVP

The Matrix Array Picture Processor (MAPP) sensor array, which has a very similar architecture to PASIC sensor described in section 2.8, consists of a 2D sensor array and a SIMD processor array [Forchheimer et al. 92, Åström 93]. The architecture of MAPP has borrowed many of the concepts of the PASIC sensor, and has improved some of the logic in the ALU by dividing it into three units: a global logic unit (GLU) for marking specific processing elements, a neighborhood logic unit (NLU) for performing operations such as left and right edge detection, and a point logic unit (PLU) for performing general arithmetic and logical operations.

MAPP2200 has been commercialized by Integrated Vision Products AB (IVP) since 1991. A system consisting of MAPP2200 camera and assembler is available from IVP. The MAPP2200 has  $256 \times 256$  sensors. In a  $1.6 \mu m$  CMOS process the chip occupies an area of  $10 mm \times 15 mm$ .

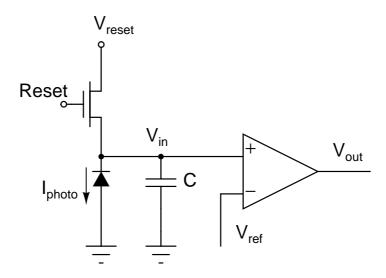

### 2.10 Forchheimer-Åström's NSIP sensor

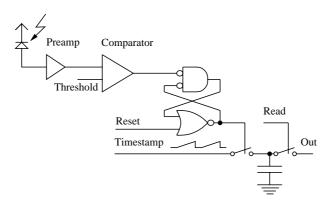

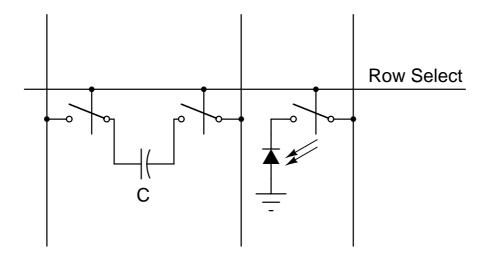

The overall architecture of Near Sensor Image Processing (NSIP) sensor is very similar to the PASIC (described in section 2.8). However, it embeds an interesting function for each pixel, which perform both an A-to-D conversion, and a 1/x compression [Forchheimer and Åström 94,Forchheimer and Åström 92,Åström et al. 96,Åström 93]. The schematic diagram of a pixel is shown in Figure 2.13. The photodetector works in integration mode. By applying the Reset signal the voltage at the input node  $V_{in}$  is precharged to  $V_{reset}$ . By turning off the resetting transistor,  $V_{in}$  charges up and when it reaches the reference voltage  $V_{ref}$  the output voltage becomes high. The time that it takes from the onset of the charging until the output voltage becomes high is related to the input light intensity (input photocurrent) by:

$$t = \frac{C(V_{reset} - V_{ref})}{I_{photo}} \tag{2.1}$$

Therefore, if the output of the detectors are sampled at some intervals, after resetting the sensor array, the intensity at each detector can be derived from the sample number at which the output of the detector has become high.

For imaging applications the readout mechanism would be complicated, as all the detectors should be read at small sampling periods and their status should be registered in a memory. However, for some image processing tasks, for example finding the position of the maximum intensity, or detecting positive or negative gradients, this method of reading the output at samll periods and performing micro-instructions on the outputs, proves more economic than the traditional methods.

Figure 2.13: The photocircuit of the NSIP sensor.

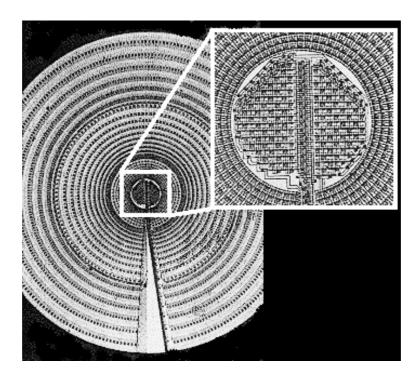

### 2.11 Sandini et al.'s foveated CCD chip

This foveated sensor has been designed by several groups from the University of Genoa, Italy, University of Pennsylvania-USA, Scoula Superiore S Anna of Pisa, and has been fabricated by IMEC in Leuven, Belgium [van der Spiegel et al. 89,Pardo and Martinuzzi 94]. It features a unique concept in the VLSI implementation of a vision chip. The foveated chip, which uses a CCD process, mimics the physically foveated (versus optically foveated, as in some birds) retina of human. Foveated vision is known to reduce the amount of information passed to subsequent processing layers significantly and therefore lends itself to image processing and pattern recognition tasks which are currently performed using uniformly spaced imagers. The foveated vision, however, has evolved concurrently with the eye motor system, where fovea focuses on areas of interest. This can be best utilized for robotic applications in which the low resolution periphery of the fovea finds areas of interest, and then directs the foveated part to get the details of those areas.

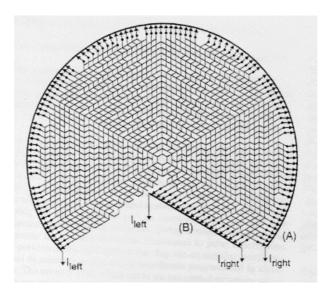

The chip has a foveated rectangular region in the middle with high resolution and a circular outer layer with decreasing resolution. The chip floor plan in Figure 2.14 shows different regions of the chip. In the circular region the chip implements a log-polar mapping of the Cartesian coordinates. This mapping provides a scale and rotation invariant transformation.

The chip has been fabricated using a triple-poly buried channel CCD process provided by IMEC. The rectangular inner region has 102 photodetectors. There are 30 eccentric circular layers in the peripheral part, each having 64 photodetectors. A part of the circles has been sliced to allow the interconnection of clock and control signals. The chip area is 11mm×11mm. In references [van der Spiegel et al. 89, Pardo and Martinuzzi 94] other aspects of the design, such as read-out structures, clock generation, simple theories about the fovea, and hardware interface to the chip are described.

Other features of this chip are:

- 8 mm diameter.

- 76 circles of 128 pixels max.

- 56 circles in "retina", with 128 pixels/circle

- 20 circles in "fovea" with less pixels:

- $-1 \times 1$  pixel

- $-1 \times 4$

- $-1 \times 8$

- $-2 \times 16$

- $-5 \times 32$

- $-10 \times 64$

- pixels have a continuous operation in time (non-integrating!)

- logarithmic intensity to voltage conversion.

Figure 2.14: Photograph of the foveated CCD retina.

### 2.12 IMEC-IBIDEM's foveated CMOS chip

The foveated CMOS chip designed by by the IMEC and IBIDEM consortium [Ferrari et al. 95b, Ferrari et al. 95a, Pardo 94], and dubbed "FUGA", is similar to the CCD fovea described in Section 2.11 [van der Spiegel et al. 89]. The rectangularly spaced foveated region in the CCD retina has been replaced by reconfiguring the spatial placement of the photodetectors. As a result of this redesign, the discontinuity between fovea and the peripheral region has been removed. In the CCD retina a blind sliced region (for routing the clock and control signals) exists. In the FUGA18 retina the need to this region has been removed by routing the signals through radial channels. Figure 2.15 shows the photograph of the central region of the foveated retina. Several versions of the FUGA chip with different sizes have been designed and manufactured by IMEC.

Figure 2.15: Central region of FUGA18 foveated CMOS retina.

### 2.13 Wodnicki et al.'s foveated CMOS sensor

Wodnicki et al. have designed and fabricated a foveated CMOS sensor [Wodnicki et al. 95], which has a high resolution central region and a peripheral region with decreasing resolution. In the central region photodetectors are uniformly spaced in a rectangle and in the periphery are placed in a circular array (See Figure 2.16). Photodetectors have been realized using circular parasitic well diodes operating in integrating mode. The area of photodetectors in the circular outer region increases exponentially, resulting in the log-polar mapping, which is known to be both scale and rotation invariant.

The chip has been fabricated in a  $1.2\mu m$  CMOS process. It has 16 circular layers in the periphery. The chip size is  $4.8mm \times 4.8mm$ . It uses a 3.3 V supply voltage and dissipates about 10 mW.

Figure 2.16: Simplified structure of Wodnicki et al.'s foveated CMOS sensor and the test system.

### 2.14 Standley's orientation detection chip

This vision chip detects the position and orientation of an object [Standley 91b]. The chip first computes moments of the image using a resistive grid. These moments are then used to find orientation and position of an object in the image.

The zeroth and first order moments of an object are defined by

$$M_{0} = \int_{0}^{x_{max}} \int_{0}^{y_{max}} m(x, y) dx dy$$

$$M_{1x} = \int_{0}^{x_{max}} \int_{0}^{y_{max}} x m(x, y) dx dy$$

$$M_{1y} = \int_{0}^{x_{max}} \int_{0}^{y_{max}} y m(x, y) dx dy$$

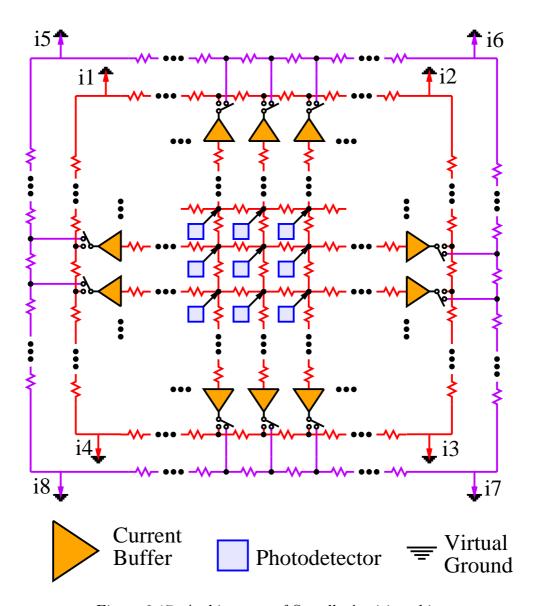

The theory and algebra from which it is postulated that using a resistive network (whose inputs are currents injected into the network, and whose outputs are the currents flowing to the periphery of the grid in four sides of the array) these moments can be computed, can be found in Standley's thesis [Standley 91a]. In this process the dimension of data is reduced by one order (from 2D to four 1D). The process of data reduction is in fact done twice. Once from within the 2D array to the 1D boundaries, and then from the 1D boundaries to four corners. The chip architecture is shown in Figure 2.17. The input to the  $30\times30$  resistive grid array is provided by a  $29\times29$  array of photodetectors. The resistive grid is implemented using passive polysilicon resistors. Photodetectors are parasitic bipolar transistors. The photo-generated currents are thresholded to eliminate the slow response time of dark pixels. The boundary of the 2D array is connected to a virtual ground. The current flowing into the boundary of the 2D array is sensed and buffered by a 1D array of current sense and buffer circuitry. The buffered current is then switched into one of two 1D resistive grids, one with uniform resistors and the other with quadratic resistors, which are linearly graded with respect to their position from origin (lower-left corner of the chip). The ends of the 1D resistive grids are finally connected to virtual grounds, where the currents can be measured. From the measured currents, the first moment of the image, for example, can be obtained using the following equations.

$$\bar{x} = x_{max} \left( \frac{i_2 + i_3}{i_1 + i_2 + i_3 + i_4} \right)$$

$$\bar{y} = y_{max} \left( \frac{i_1 + i_2}{i_1 + i_2 + i_3 + i_4} \right)$$

The chip has been fabricated in a  $2\mu m$  CMOS process in an area of  $7.9mm \times 9.2mm$ , and contains an array of  $29 \times 29$  cells occupying a total area of  $5500\mu m \times 5500\mu m$ .

Figure 2.17: Architecture of Standley's vision chip.

### 2.15 Harris et al.'s Resistive Fuse Vision Chip

In [Harris et al. 90, Harris 91, Harris et al. 89] the concept of resistive fuses and a vision chip based on the resistive fuse idea are described. Resistive fuses are two-port nonlinear elements in which the I-V relationship is linear for small values of the voltage across the element, and the current falls as the voltage increases. If this element is used in resistive smoothing networks instead of the linear resistors, for small differences between the inputs, the network performs a smoothing operation. But for abrupt spatial changes and large differences, the resistor is virtually turned off. Believing that large differences only occur at places where discontinuities exist, the resistive fuse network is capable of segmenting regions separated by abrupt intensity changes, and smoothes other regions with less variation. It should be noticed that due to the introduction of a nonlinear element with a negative I-V region, the network can have several local minima and may not converge to the global solution. A simple treatment is to change the biasing of the fuse in such a way to start from the original linear resistor and gradually vary the bias to end up in the global minimum.

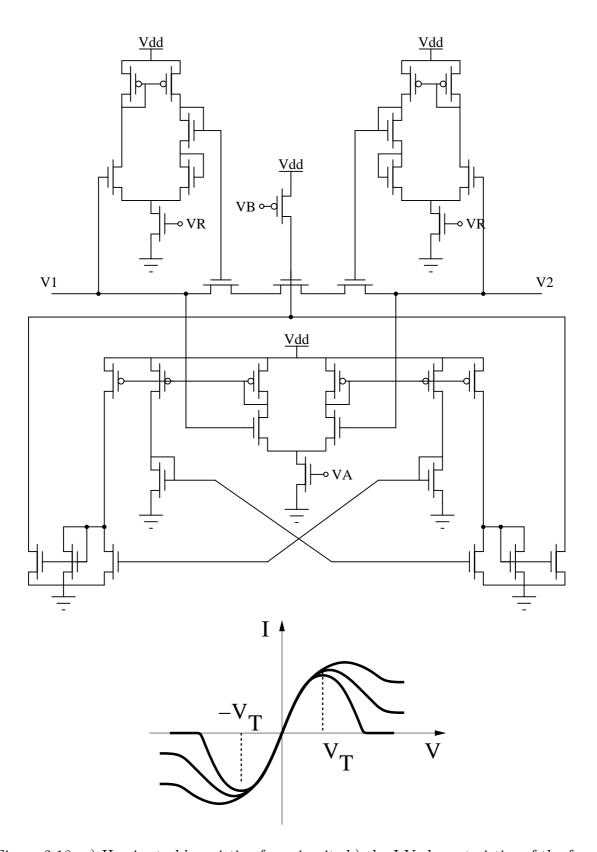

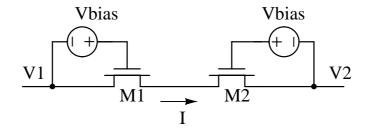

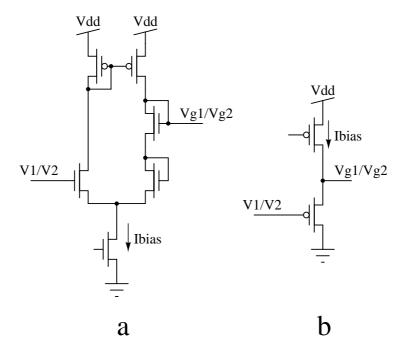

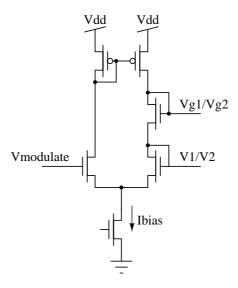

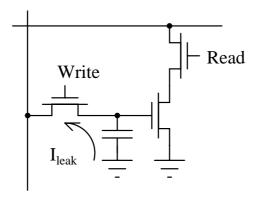

The circuit and I-V characteristics of the fuse are shown in Figure 2.18. The slope of the I-V curve in the linear region, and the threshold value at which the curve starts falling down are determined by the bias voltages  $V_A$ ,  $V_B$ , and  $V_R$ . It can be easily seen that the upper portion of the circuit is the same as the horizontal resistor described in [Mead 89b].

A similar concept has been followed in [Yu et al. 92]. A new circuit introduced in [Yu et al. 92] is shown in Figure 2.19. Compared with the previous circuit it uses fewer transistors, but the linear range of the resistor is small and uncontrollable which makes it unattractive. The transition from linear to cut-off region is also sharper in this circuit.

Harris et al. have designed and fabricated a  $20 \times 20$  array of this fuse network and illustrate promising results from some simple tests.

Figure 2.18: a) Harris et al.'s resistive fuse circuit. b) the I-V characteristics of the fuse.

Figure 2.19: Yu et al.'s resistive fuse circuit.

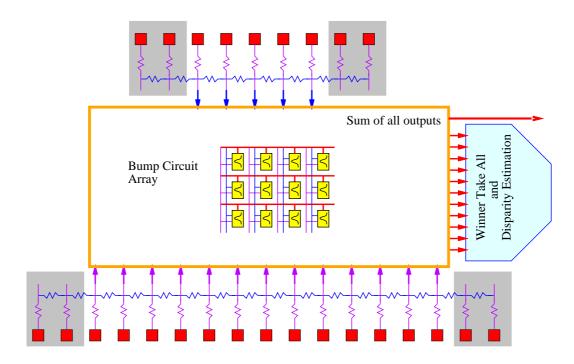

## 2.16 DeWeerth's Localization and Centroid Computation Chip

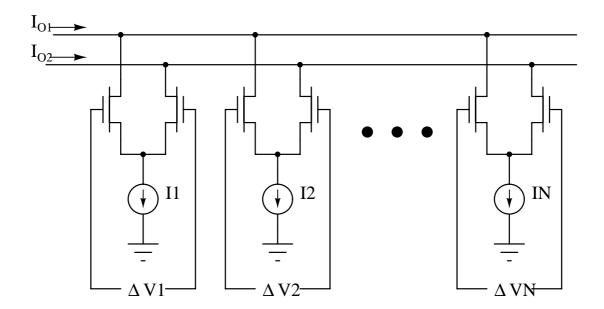

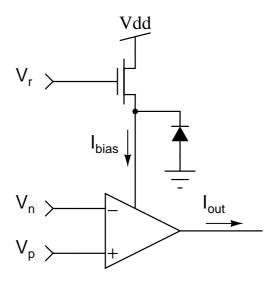

DeWeerth has implemented a centroid detection chip [Deweerth 92] based on an aggregation network shown in Figure 2.20. Using this circuit an output current of the form

$$I_{O1} - I_{O2} = \sum_{n} i_n \tanh\left(\frac{\Delta V_n}{2U_t}\right)$$

is obtained. In order to use this circuit for spatial centroid detection, a spatially-sweeping reference voltage is produced at one input of the differential pairs. This is simply done by a resistive voltage divider with its ends connected to reference voltages,  $V_0$  and  $V_N$ . The other input of the differential pairs are all connected together and connected to the output of the circuit. Photocurrents are presented as the biasing current of the differential pairs. In the actual implementation described in [Deweerth 92] the input transistors of the differential pairs are realized using bipolar transistors to reduce the effects of device mismatch. Polysilicon resistors have been used for the voltage divider.

Obviously, the nonlinearity of the tanh function affects the operation, if proper assumptions or constraints are not made. It is reasonably assumed that the voltage difference across each resistor,  $(V_N - V_0)/N$ , is very small. This can easily be satisfied by a choice of reference voltages. An analysis for a simple case of constant background illumination and constant-width-and-intensity object is given in [Deweerth 92].

The  $160 \times 160$  array of this centroid detection chip has been realized in a  $2\mu m$  BiCMOS process in an area of  $6.8 mm \times 6.9 mm$ .

Figure 2.20: DeWeerth's spatial aggregation circuit.

Figure 2.21: DeWeerth's spatial centroid detection circuit.

### 2.17 Ward & Syrzycki's Receptive Field Sensors

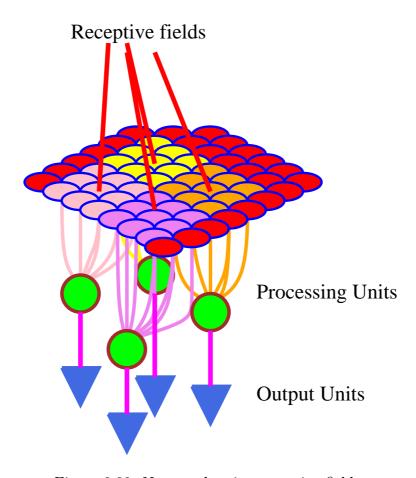

In [Ward and Syrzycki 95, Ward and Syrzycki 93, Ward et al. 93] Ward & Syrzycki describe vision sensors based on the receptive field concept. Receptive fields are regions over which several neighboring photoreceptors provide input to processing units. Therefore, a receptive field consists of several photodetectors, a processing unit, and an output unit. There may or may not be overlap between contiguous receptive fields. A sensor with non-overlapping receptive fields is shown in Figure 2.22. In this figure each nine receptors constitute a receptive field.

Based on this concept a Sobel edge detector has been implemented in a chip, where the operators in x and y direction are given by

$$S_x = \begin{bmatrix} -1 & 2 & -1 \end{bmatrix} \qquad S_y = \begin{bmatrix} -1 \\ 2 \\ -1 \end{bmatrix}$$

(2.2)

The weighting required for the Sobel operators is done using current mirrors. In the implemented chip each edge operator collects input from its eight nearest neighbors.

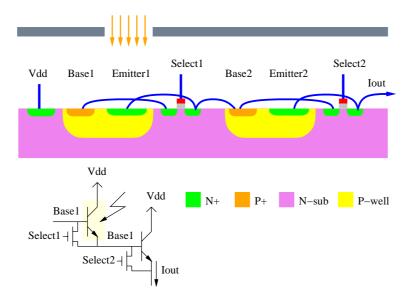

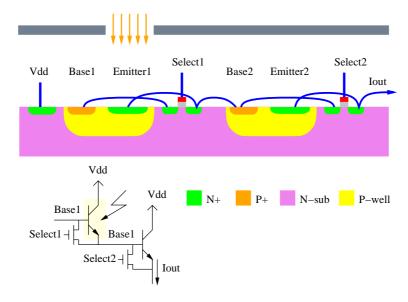

The reference [Ward and Syrzycki 93] also provides information on a multi-sensitivity photodetector. This detector is a parasitic vertical bipolar between diffusion, well, and substrate. By connecting a MOS transistor to base and emitter of the bipolar transistor the gain of the photodetector can be changed. By using another bipolar transistor in a darlington structure the current gain can be boosted once more. However, the dynamics of such a structure significantly degrades at low light levels. The main advantage of using this structure is that the output current can be limited to a range of a few decades, by activating both bipolar transistors at very low light intensities and inactivating both transistor at higher intensities. The cross section of this structure is shown in Figure 2.23.

Figure 2.22: Non-overlapping receptive fields.

Figure 2.23: Ward-Syrzycki's multisensitivity photodetector.

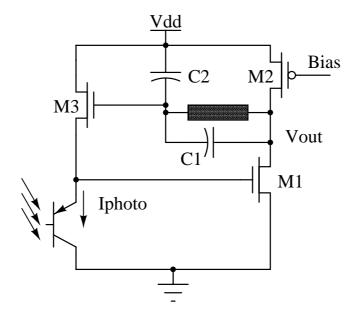

#### 2.18 Wu & Chiu's 2D Silicon Retina

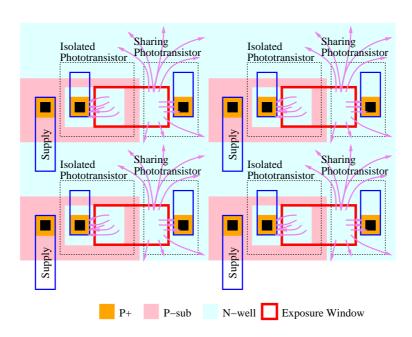

This silicon retina subtracts the original image from a spatially smoothed version of the image, therefore it eliminates the local average and enhances edges. This retina, however, uses "well" resistance in the resistive network used for smoothing operation [Wu and Chiu 95, Wu and Chiu 92]. Each cell consists of two parasitic phototransistors; one which is properly isolated from other transistors, and one whose base is shared with its neighboring phototransistors of the same type. The photogenerated electron-hole pairs in the latter can therefore diffuse to its neighbors, resulting in a smoothing function. The simplified layout of four cells of this retina is shown in Figure 2.24.

Due to the large stray capacitance and resistances associated with the base of sharing phototransistors, the smoothing operation will have a delay. Hence, a crude motion detection is also obtained.

The major drawback of such a retina is the uncontrollability of both the smoothing constants and the delay, which heavily depend on the process used, the size, and the shape of the well regions being shared by the sharing phototransistors.

A 32×32 array of this silicon retina has been fabricated in a  $0.8\mu m$  DPDM CMOS process. Each cell occupies an area of  $60\mu m \times 60\mu m$ .

Figure 2.24: Simplified layout of Wu-Chiu's retina.

### 2.19 Nilson et al.'s Shunting Inhibition Vision Chip

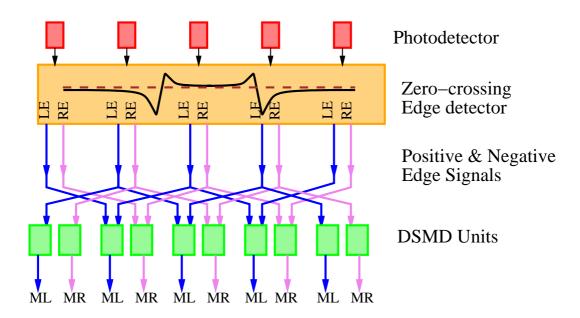

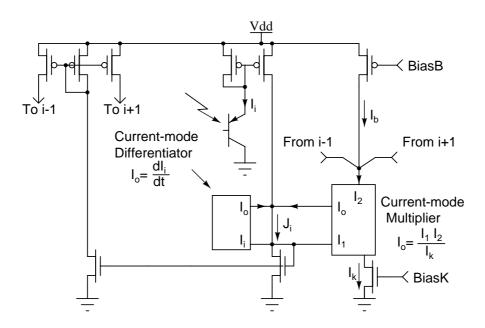

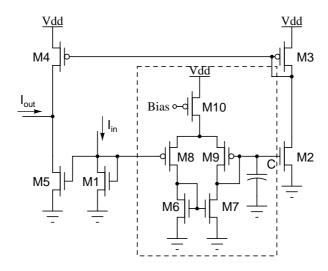

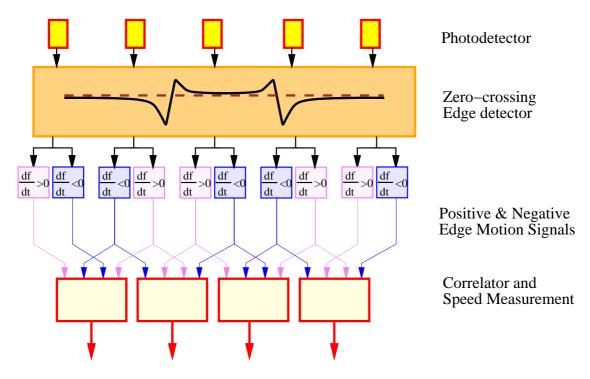

"Lateral inhibition is one of the overlapping mechanisms used by many creatures to extend their visual capabilities without requiring additional processing by the brain" [Nilson et al. 94]. In lateral inhibition a cell receives negative weights of the *inputs* of its neighbors. It has originally been developed as a model for biological vision, but it has formed a rigorous mathematical background over the years [Bouzerdoum and Pinter 91,Bouzerdoum et al. 92]. In shunting inhibition the negative weight from neighbors also contain a multiplicative factor of the output of its neighbors, i.e.

$$I_{out,n} = I_{in,n} - kI_{in,n+1}I_{out,n+1} - kI_{in,n-1}I_{out,n-1}$$

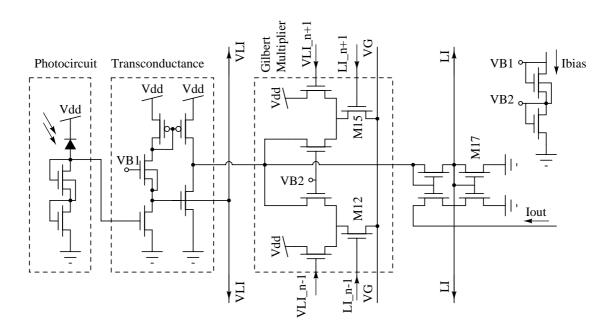

This vision chip designed by Nilson et al. implements a shunting inhibition network using current mode circuits. Current multiplication is performed by a four-quadrant Gilbert multiplier. The schematic of the cell is shown in Figure 2.25. VLI is the term proportional to the input, and LI is the term proportional to the output. The weight factor k is obtained by sizing the transistors M12 and M15 with respect to M17. The control voltage VG gives another degree of controllability over the weight factor because the source of M17 is connected to the GND node, but the source of M12 and M15 are connected to VG.

The designed chip which uses a  $1.2\mu m$  p-well CMOS process has a one-dimensional array with 24 cells.

Figure 2.25: Nilson et al.'s shunting inhibition circuit.

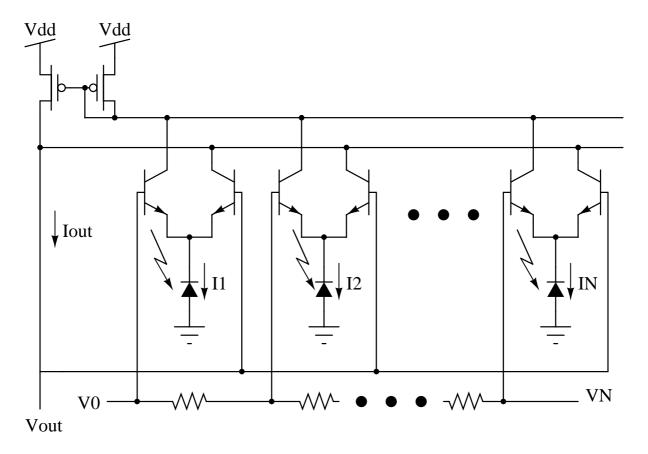

### 2.20 Keast & Sodini's CCD/CMOS Imager and Processor

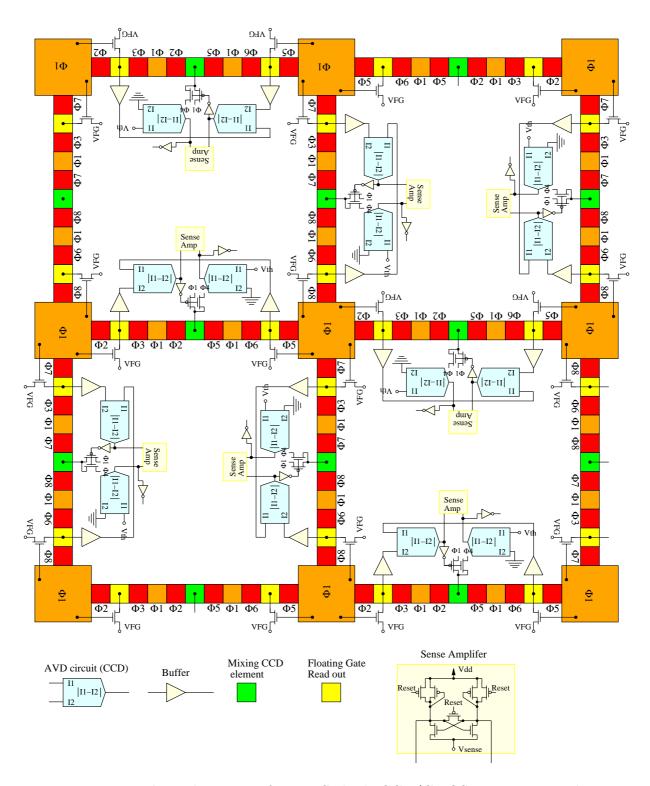

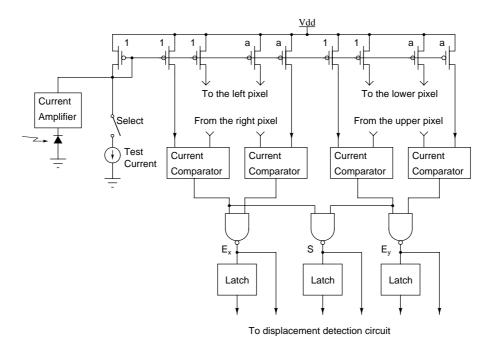

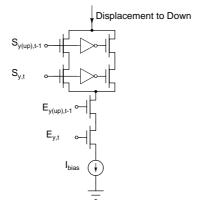

The 2D CCD/CMOS imager and processor designed by Keast and Sodini [Keast and Sodini 92, Keast and Sodini 93, Keast and Sodini 90] combines the CCD imager and CMOS processing blocks to perform smoothing and segmentation on the input image. A simplified schematic of several cells of the chip are shown in Figure 2.26. Each cell comprises a CCD photodetector, and several other CCD elements. A CCD/CMOS circuit also computes the difference between two neighbors. If the difference does not exceeds a predefined threshold, the gate of a mixing CCD device (shown in green color) is connected to a proper clock to perform a smoothing operation. Otherwise, the gate of the mixing CCD device is connected to another clock, as a result of which no smoothing is performed. Calculating the difference and comparing it with a threshold is done using the absolute value of difference circuit (AVD) described in section 4.2. The smoothing operation is performed by a fill-and-spill CCD circuit described in section 3.12.

The fabricated chip comprises a  $4\times4$  array on cells. It is designed in a  $2\mu$ m buried channel CCD/CMOS process.

Figure 2.26: The architecture of Keast-Sodini's CCD/CMOS segmentation chip.

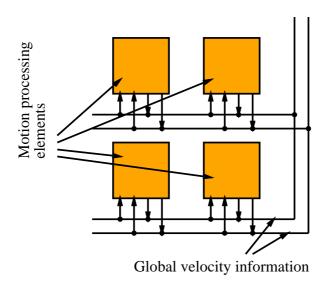

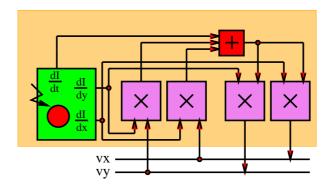

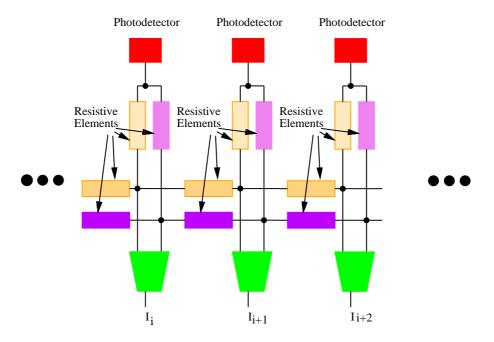

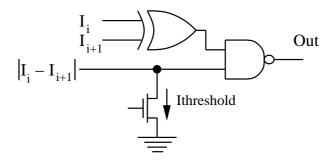

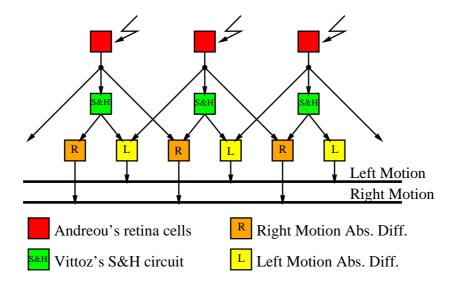

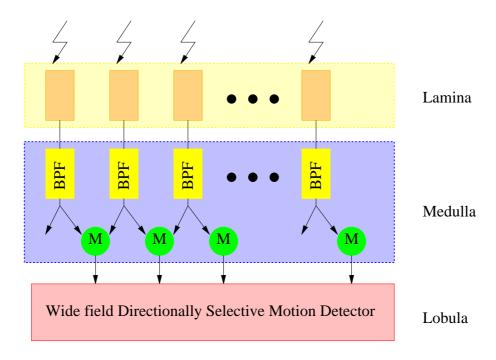

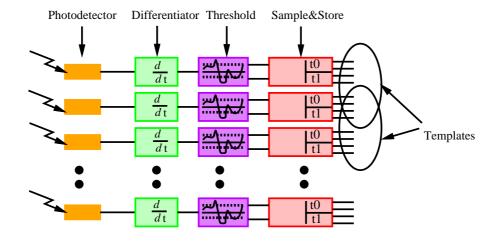

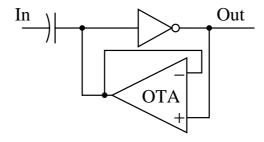

### 2.21 Mitsubishi Electric's CMOS Artificial Retina with VSP